主题中讨论的其他器件: ADS1299、 ADS1278

您好!

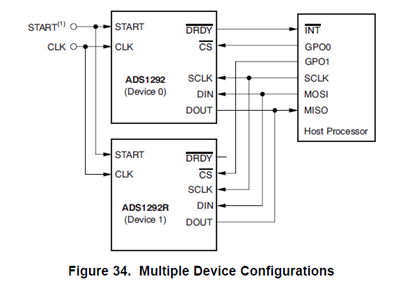

我想同时使用两个 ADS1292。 现在、我要进行 PCB 布局、我对 PCB 尺寸和层数有严格的要求。 我正在寻找简化两个 ADS1292和微控制器之间连接的方法。

为此、我有两个想法:

-我可以共享 CLK 和 SCLK 信号吗?

-我能否只使用一个 DRDY (由于两个 ADS1292已同步(共享启动引脚和 CLK)、那么新数据应始终同时可用)? 我在这个论坛中已经读到过、几个 ADS1292的 DRDY 引脚不能连接在一起、但是我可以将第一个 ADS1292 DRDY 引脚连接到微处理器、并使第二个 ADS1292 DRDY 引脚悬空、对吧?

谢谢