请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

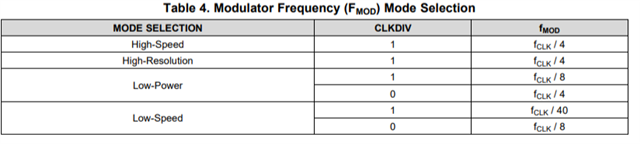

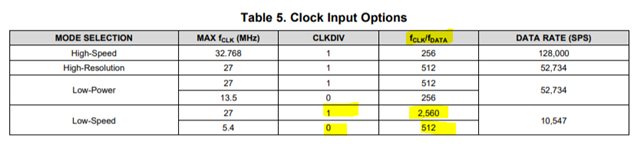

器件型号:ADS1278-SP 大家好、我正在与客户一起使用此器件。 它们以5MHz 的 FCLCK 运行(并且 CLKDIV=0)。 遗憾的是、它们必须降额至80%才能满足其规格、因此最大5.4Mhz x 0.8为4.3MHz。 它们可能必须更改为 CLKDIV=1、最大 FCLK 为27MHz。 当它们在 CLKDIV=1时仍以5MHz 运行时、会发生什么情况? CLKDIV 0和1之间的内部时序等是否相同、因为工作频率保持在5MHz?

提前感谢。