大家好、

我是第一次使用 ADS1282-SP、我必须设计用于控制它的 FPGA。 作为后一个 OTP 器件、我没有错误的空间。

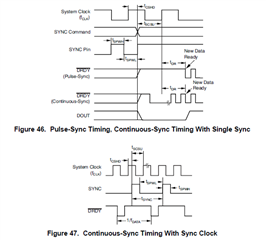

我的目的是在连续读取数据(RDATAC)模式和脉冲同步模式下使用 ADS1282-SP ADC。

数据表报告了两个图、用于比较脉冲同步和连续同步读取模式。

在连续同步模式下、可以使用类似时钟的脉冲信号、同时尊重 ADC 时钟的所有限制。 非常清楚。

我需要清楚地了解的是同步脉冲在脉冲同步模式下工作时的形式。

ADC 的 SYNC 输入应先驱动为高电平、然后驱动为低电平、再驱动为高电平(w.r.t 时序限制)、 还是 应仅驱动为低电平到高电平以触发新的转换?

SYNC 引脚是否应在我读取数据时始终保持高电平、并且 仅在我不需要读取 ADC 转换的数据输出时才被驱动为低电平? 换句话说、SYNC 引脚是否会影响启用/禁用/DRDY 输出?

正在等待您的回复。

此致、

Daniele Lippi