您好!

我仍在另一个新项目中使用您的 ADS1675 (出色的器件)。

在过去的项目中、我将器件用作低速(1MSPS)、32MHz 外部时钟、CMOS 输出接口、但在这个新项目中、我必须在1MSPS 和2MSPS 之间选择数据速率。

为了简化 FPGA 设计、我决定为这两种应用使用 LVDS 接口和内部 SCLK 生成。

常规设置(硬接线)如下:

CS ="0"(单个器件);SCK_SEL ="0";LVDS ="0";LL_Config ="1";FPATH ="0"。

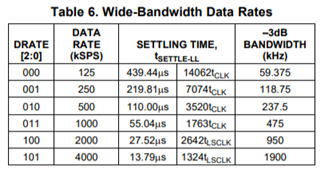

对于1MSPS、DRATE 被设定为'011'、而对于2MSPS、DRATE 被设定为'100'。

START 引脚在每次配置更改时都处于"选通"状态、然后保持高电平以进行连续采集。

对于1MSPS、提供给 ADS1675的 CLK 为24MHz、借助内部 PLL x1、在 SCLK 引脚上提供正确的24MHz。

对于2MSPS、提供的 CLK 为16MHz、借助内部 PLL x3、可在 SCLK 引脚上提供正确的48MHz。

为了测试该设计、我们提供了一个50 KHz 的模拟连续正弦波形。

当我们转储样本时、恢复的波形对于两个比特率似乎都是正确的。

但我们在 DRDY 时序上有意外行为。

由于由 jpg DRATE_3 (数据速率='011'、1MSPS)分页、我们观察到 DRDY 发生的时序为~ 1.3us 而不是1us (24MHz 时为32个 SCLK 周期 、而不是24个)。

由于 jpg DRATE_4 (数据速率='100'、2MSPS)具有 showns、因此 DRDY 发生的速率为1us (48个 SCLK 周期、而不是24个周期)。

我们还在不同的设置中对其进行了测试、如您在 jpg DRATE_5中所见。

在本例中、DRATE 为'101'、对应于4MSPS、但我们仍在 CLK 引脚上提供16MHz 频率。

如您所见、此设置似乎对应于正确的2MSPS 行为:SCLK 引脚为48MHz、DRDY 的发生频率为0.5us、SCLK 周期的计数器对应于 DRDY 的发生频率为24。

我们错过了什么?

提前感谢

Andrea