我们在相同的 CLK 信号上运行其中三个 ADC 彼此同步。 图1显示了每个 ADC 的布线方式(它们都是相同的)。 ADC 的奇怪间歇性读数是我开始这项调查的原因。 有时、其中一个 ADC 会产生一个我不会看到的读数。 在我的整个调查中、我发现 ADC 的 DRDY 引脚"不同步"。 我的意思是说、每个 ADC 的 DRDY 线路将同时变为低电平、并按其应有的方式进行同步(图2)、直至触发它们彼此之间变为低电平大约80ns。 然后、触发再次发生、并且现在间隔为120ns (此处实际时间增量并不重要、只是 DRDY 线不同步)。 这一过程会重复、DRDY 线路彼此之间的距离会越远。 图3显示了来自两个 ADC 的 DRDY 信号不同步。

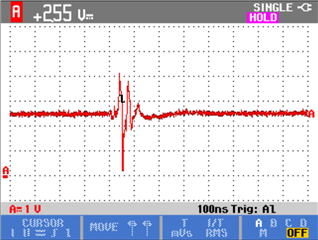

我发现的以及我和我的团队认为"不同步触发器"是 VREFP 线路上的瞬态电压尖峰/下降。 它持续约100ns、基准电压尖峰超过芯片的最大电压限值、并且也会下降到相当低的值。 图4是该 VREF 瞬态的一个示例。 我们目前正在尝试摆脱这种瞬态、但我仍然想了解您的芯片及其同步问题、以了解我的理论是否真实。

*我们电路中的 VREFP 电压为2.5V、瞬态尖峰高达几乎4V。 根据数据表、VREFP 线路上的最大电压为3.3V。 这种违规行为是否会导致 ADC 失去同步?

*瞬态也会将 VREF 电压降至接近1V、这是否会导致 ADC 以某种方式复位、从而失去同步?

*这些奇怪的读数是否是数据表第8.3.5节中超出范围的系统监控器的症状、而不是同步丢失?

无论这种不同步事件的原因是什么、我都找到了一个带有软件的"带辅助"解决方案。 通过定期将所有3个 ADC 的 START 引脚置于低电平、然后再次置于高电平、DRDY 信号会进行同步恢复。 不同步触发事件仍会发生、DRDY 信号仍会定期从该事件中退出同步、但它们会在出现任何问题之前快退到同步中。 此解决方案是通过阅读数据表的第8.4.3节找到的、我确保表13满足计时要求 tw (STL)。

借助这种带辅助功能、ADC 可以运行数小时、而不会产生任何奇怪的读数。 到目前为止,我还没有看到任何奇怪的读数。