主题中讨论的其他器件:ADS8505、 ADS8509

在使用 ADS8508IBDWR 的应用中、输出数字代码似乎会受到一些干扰。

调查表明、问题可能与所选的钽电容器有关。

1) 1)是否确实需要钽电容器-如 DS 所示、电容、REF、VANA?

2) 2)如果需要、除了电容外、是否还有任何需要考虑的参数?

此致、

Darren

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Darren、您好!

REF 和 VANA 引脚可以使用陶瓷电容器、并且应提供比钽更好的性能。 但是、CAP 引脚对总 ESR 很敏感。 数据表建议电容引脚上的电容器的最大 ESR 为3 Ω。 许多钽电容器的值将高于此值。 您可能希望使用 ESR 更低的钽电容器、或将陶瓷电容器与1欧姆电阻器串联、以更类似于高质量、低 ESR 钽电容器。

此致、

Keith Nicholas

精密 ADC 应用

您好、Keith、

很抱歉 Necro 此帖子。

但我发现 了这篇 E2E 帖子 (5年前)、内容是针对 ADS8505 (16位版本的 ADS8508?) CAP 引脚上的钽 电容器是不必要的;陶瓷电容器是可以的。 这是因为 ADS8505设计不依赖于 ESR。 在该帖子中、"Wu JW"表示、我的客户也确认、在电容器上使用低 ESR 陶瓷电容器实际上会产生更好的 ADC SNR。 查看数据表(ADS8505)中的图17、可以看到、在整个 ESR 范围内、SNR 也相当稳定。

对于我的客户来说、向陶瓷电容器实际添加~1Ω Ω 串联电阻会略微降低性能。

但是、与上述情况相矛盾...

我找到 了此文档 中的一个专用基准、该基准电压用于显示陶瓷电容与钽电容;

但它也建议~1.5Ω Ω 的 ESR 和钽电阻。

总结问题:

1) 1)我们为什么(如果可能、请提供有关机制和图形的详细信息)需要使用"ADS8508/9钽?

2) 2)我~1Ω、如果需要 Δ V ESR、"太小"和"太大"可能会对噪声和稳定性产生不利影响。 为什么?

根据我的经验、以下两个问题似乎是...想法?

a:ESR 过小、基准输出缓冲器无法驱动2.2uF 电容器;导致稳定性问题

B. ESR 过大、您将极点拉入并降低相位裕度、从而导致稳定性问题

此致、

Darren

您好 Darren、

在数据表中建议使用钽电容器的原因是、当最初发布 ADS8505时、2.2uF 陶瓷电容器在小型封装中不能广泛使用。

由于钽电容器很常见、因此稳压器电路通常通过内部补偿来与一系列 ESR 配合使用、因此可以使用许多钽电容器类型。 在本例中、我的建议是保守的、因为我不确定 CAP 引脚是否会在 ESR 为0欧姆时保持稳定。 您发现的旧帖子确认了该特定 ADC 不需要外部 ESR 电容。

因此、是的、对于 ADS8505、可以使用陶瓷电容器代替所有钽电容器。

关于具体问题、如果 ESR 过低且没有内部补偿、外部电容将产生具有输出级阻抗的极点、从而减小会导致额外振铃或完全振荡的相位裕度。 同样、这可以通过内部补偿来消除、这就是大多数现代基准和 LDO 的设计方式。

根据器件内部的补偿设置方式、ESR 过大也会导致稳定性问题、但更常见的情况是、电容器根本不会帮助在负载瞬态较大的情况下维持稳定的输出电压。

此致、

Keith

您好、Keith、

[引用 userid="3754" URL"~/support/data-converters-group/data-converters/f/data-converters-forum/1131257/ads8508-selecting-capacitors-for-cap-ref-vana/4224421 #4224421"]因此、是的、对于 ADS8505、可以使用陶瓷电容器代替所有钽电容器。

[/报价]客户真的需要对 ADS8508/ADS8509进行评论。

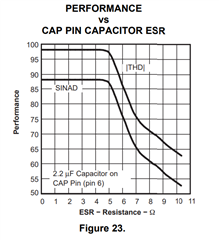

您对我的第一次答复中的图23表示 SINAD/THD 即使低至0Ω Ω ESR 也是最佳/稳定的。

数据表中还仅显示"将 ESR 保持在3Ω Ω 以下至关重要"-这与图23一致。

3Ω 这一点、如果我错了、请纠正我的问题、但我理解只要 ESR 在 PVT 和寿命期间保持稳定(<1 μ V)、那么就没有最低要求、而 MLCC 是一个可行的高性能稳定选项、这可能在15年前就没有。

我是否正确理解了这一点? (我想陶瓷与钽相比、振动噪声拾取仍然存在问题...)

如果在发生意外情况时、此器件确实需要一些最小 ESR (未在数据表中定义或上述第一个帖子中的图23中定义)、那么您能否向客户确认器件的稳定性/运行所需的最小 ESR 是多少?

~3Ω 指出、如果在 MLCC 和钽之间唯一真正需要注意的是为 MLCC 添加一个串联电阻器、那么为该1 μ A 甜蜜点进行设计就会稍微困难一些。

它们还证实了 ESR 更低(MLCC)的性能优于钽电阻器或 MLCC + 1Ω Ω 电阻器。

此致、

Darren

您好 Darren、

随着 ESR 的增加、基准缓冲器的相位裕度减小、稳定所需的时间更长。 ADC 的基准输入是开关电容器、基准缓冲器将其视为阶跃输入负载电流变化。 在相位裕度较低的情况下、CAP 引脚将振铃并需要很长时间才能稳定、这将在 ADC 频谱中显示为谐波失真、从而降低 THD 和 SINAD。

TI 高精度实验室- ADC 系列更详细地讨论了这些效果。 请观看本演示、其中讨论了缓冲引用的使用。 对于 ADS8509、增加的 ESR 会降低缓冲器的效率、从而导致更高的失真。

此致、

Keith