Other Parts Discussed in Thread: ADC12J1600

大家好、

我正在尝试在 FPGA 上开发一种算法、以处理 ADC 采样的数据。 我们使用 TI 的 ADC12J1600和 Xilinx 的 KC705、也使用 TI 的 TSW14J10来连接这两个板。

下面是 ADC 的配置:

抽取= 4;

LMFS = 4222;

K = 16;

参考时钟= 200MHz;

器件时钟= 100Mhz;

以下是输出数据格式:

我已根据 Xilinx 的 JESD204硬件演示和 JESD204示例设计创建了一个4通道 JESD204B RX 项目、原理图如下:

RX 内核的配置与 ADC 的设置相匹配。 考虑到项目中只有一个 RX 内核、我选择将共享逻辑包含在内核中。

通过使用 VIO、我们可以正确执行寄存器读取/写入访问。 以下是 AXI 控制寄存器配置:

0 => x"8008", --地址 x008

1 => x"0000"、 --数据 x0000_0001 启用通道对齐

2 => x"0001"、

3 => x"800C"、 --地址 x00C

4 => x"0000"、 --数据 x0000_0001 [0]启用加扰

5 => x"0001"、

6 => x"8020", --地址 x020

7 => x"0000"、 --数据 x0000_0001 F (每帧八位位组)= 2.

8 => x"0001"、

9 => x"8024"、 --地址 x024

10 => x"0000"、 --数据 x0000_000f K (每多帧数)= 16

11 => x"000f"、

我使用 GPIO LED 来检查接口信号、结果如下:

LED[4]闪烁、显示 FPGA 可以接收参考时钟和全局时钟;

LED[3]打开、显示系统时钟已锁定、并为 AXI 控制器生成200MHz 时钟;

LED[2]打开、显示 JESD204B 接收器可以生成 RX_aresetn 信号、该信号用作数据解调块的复位信号;

LED[1]打开、显示 TX_RESync 有效、并发送到 ADC;

LED[0]打开、显示 Rx_resync 已生效、这是接收器生成的同步信号;

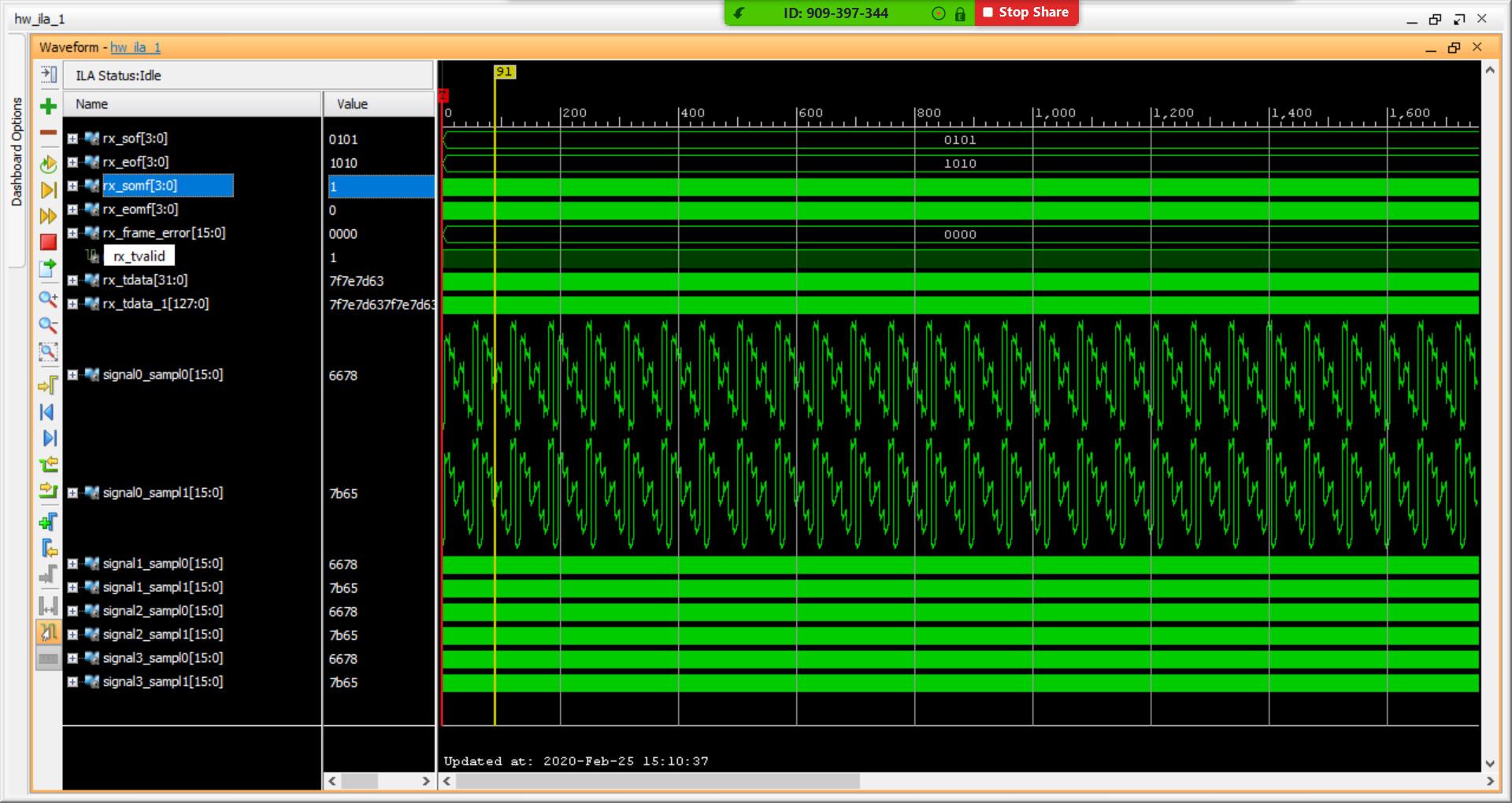

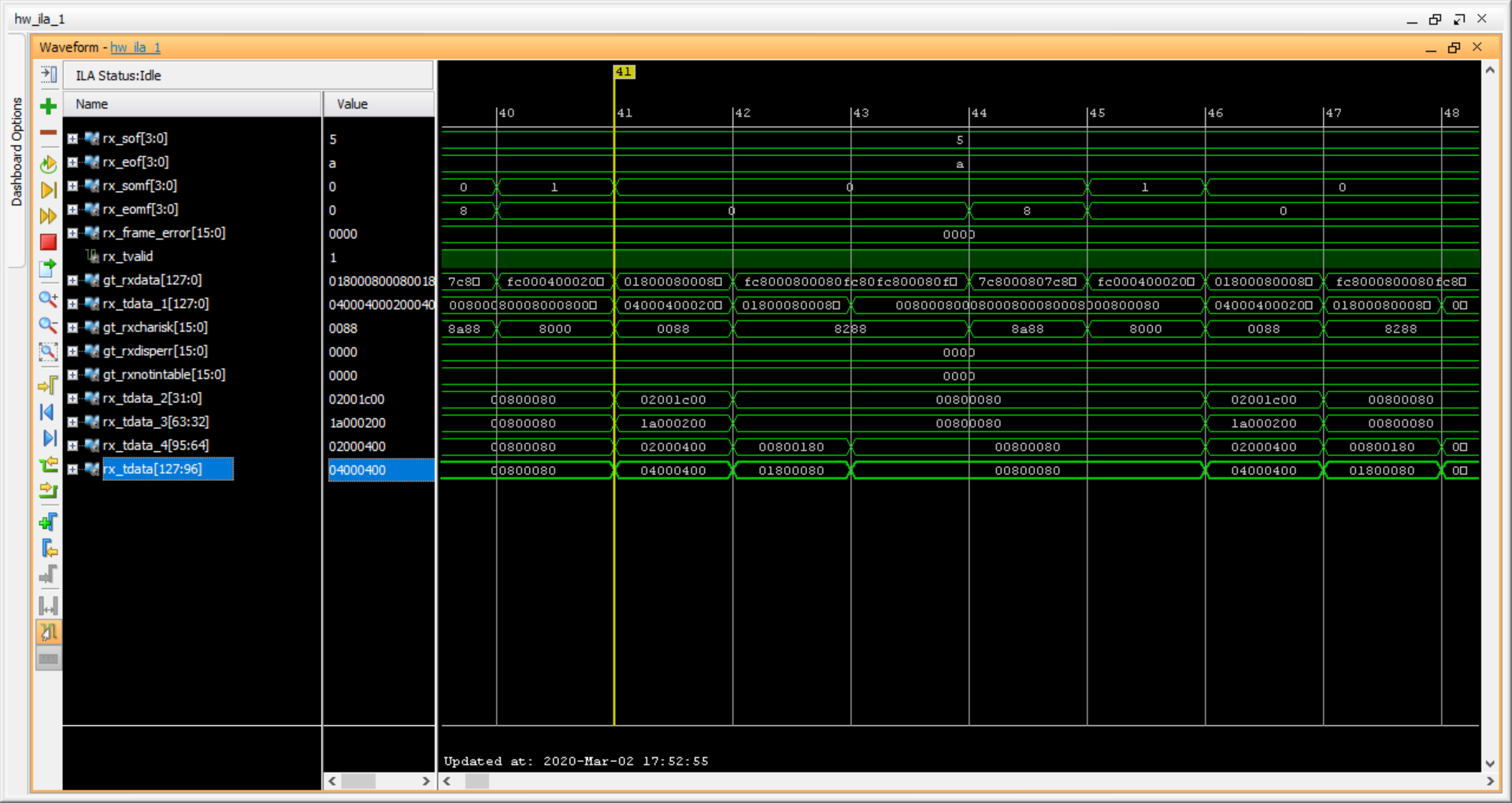

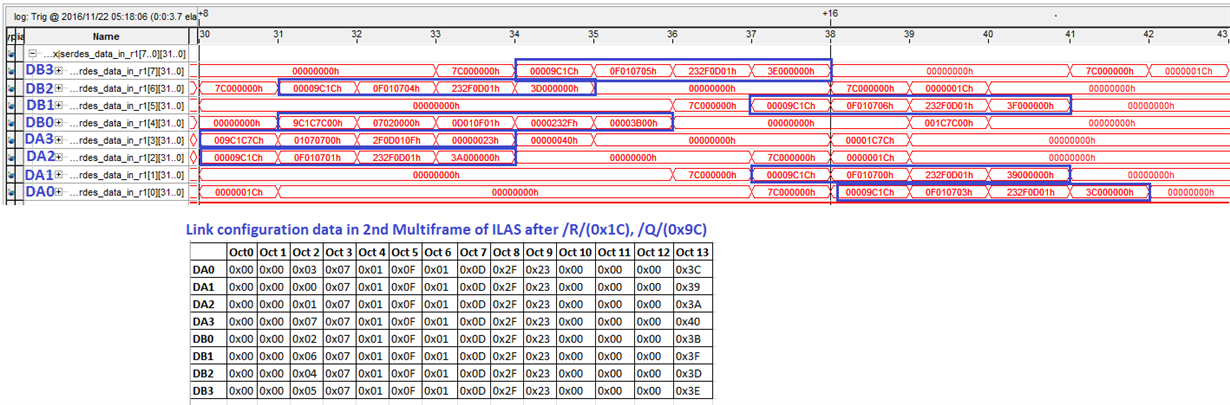

数据由 ILA 捕获、我们已将 ADC 设置为斜坡测试模式并正常、结果如下:

(1)斜坡测试模式--每条通道发送一个相同的八位位组流,该二进制八位位组流从0x00递增到0xFF 并重复。

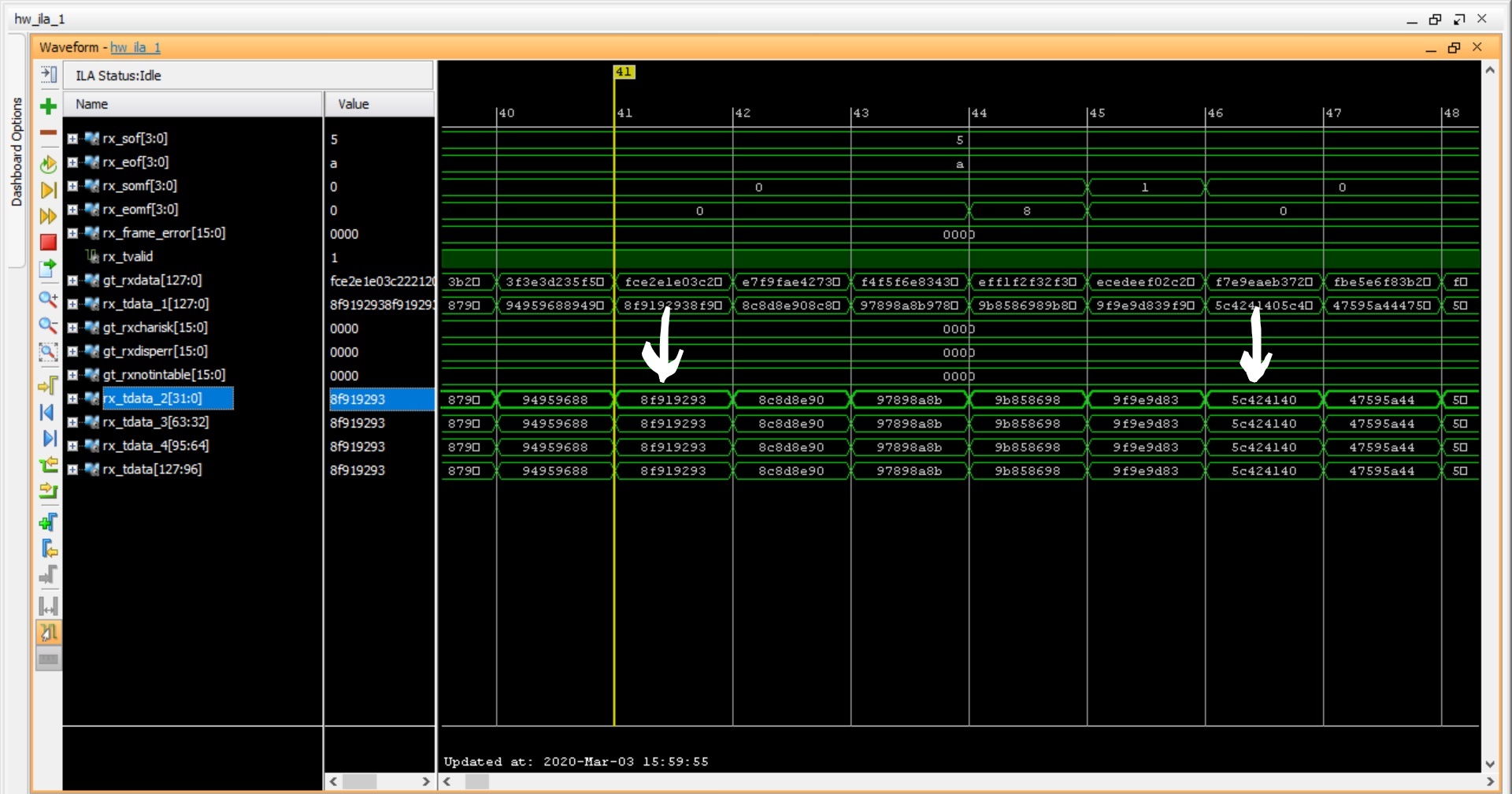

来自4个通道的数据完全相同、这是合理的、因为 ADC 正在向每个通道发送相同的八位位组流。 但是、现在捕获的数据的值不正确。

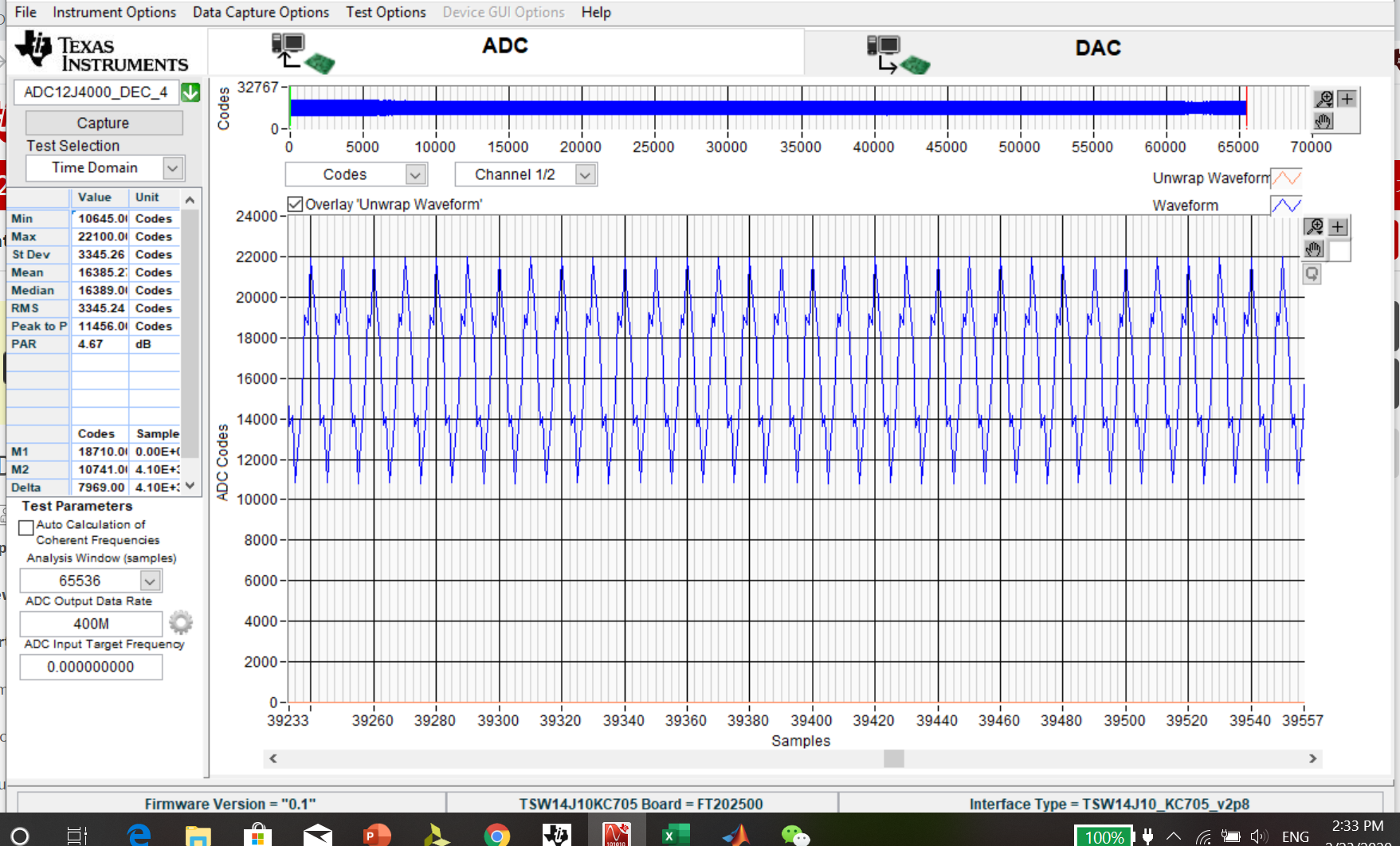

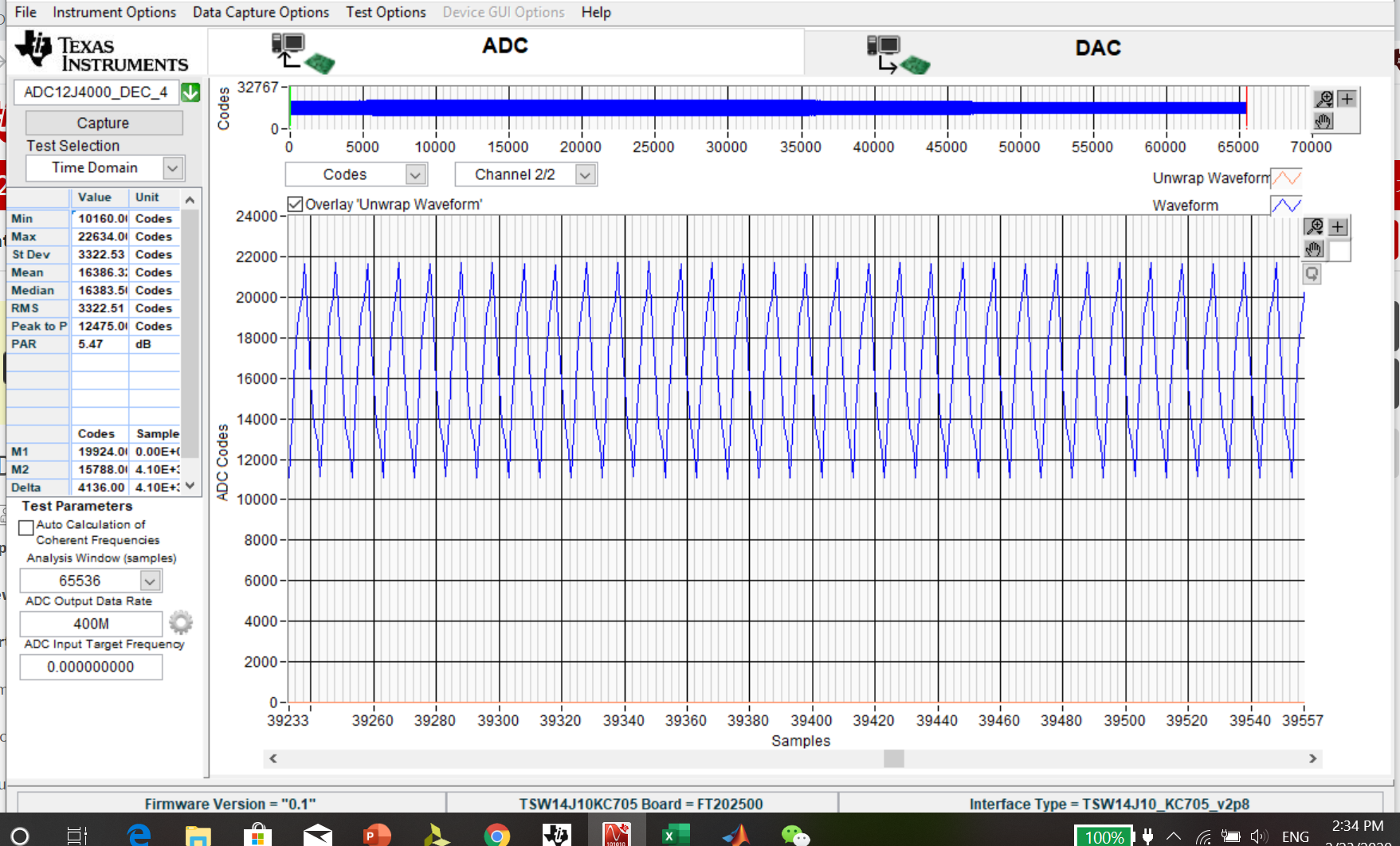

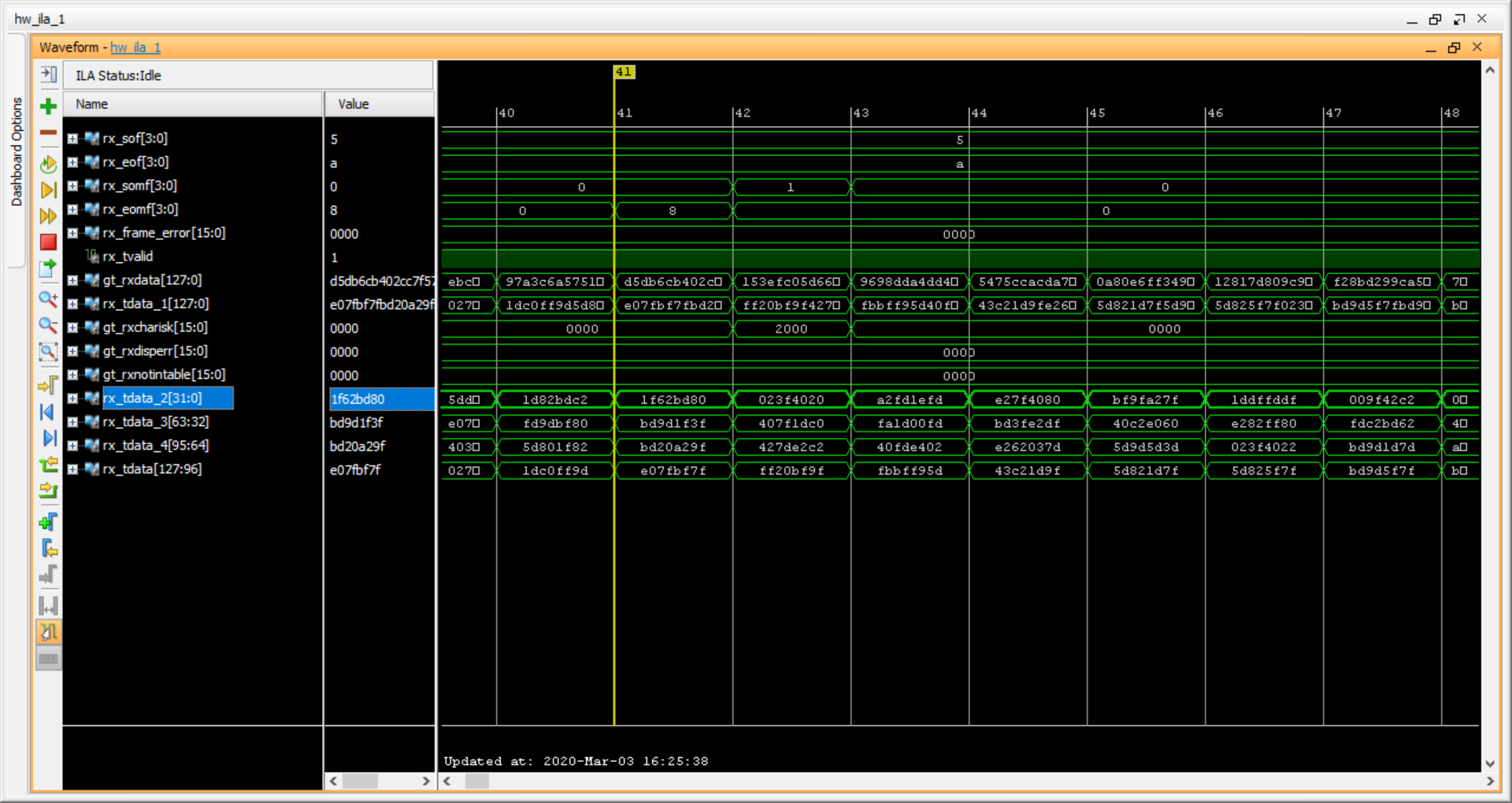

(2)正常模式–ADC 对函数发生器的正弦波进行采样。

传输层映射后收集的数据不正确。 但是、信号 RX_START_FRAME、RX_END_FRAME、RX_START_OW_MULTIFRAME、RX_END_OL_MULTIFRAME 的结果符合 JESD204示例设计的仿真结果。

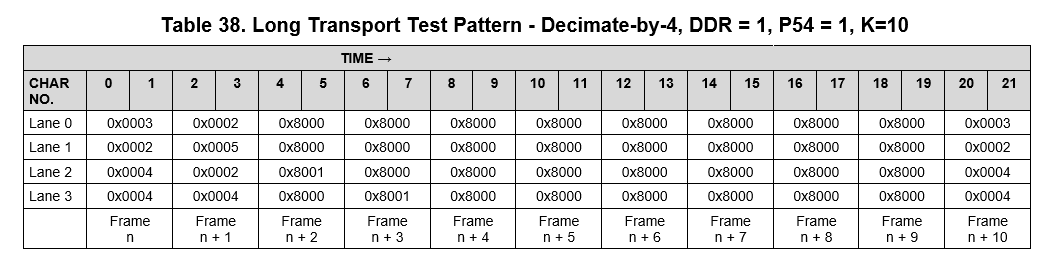

我认为 JESD204 IP 内核以正确的方式运行、所以我对错误原因的猜测是我没有正确映射 Rx_DATA[127:0]、这是我根据 ADC 的输出数据格式所做的:

//通道0

signal0_sampl1 <= rx_tdata[31:17]; lane0上每秒采样的//数据位

signal0_cntrl1 <= rx_tdata[16]; lane0上每秒采样的//控制位

signal0_sampl0 <= rx_tdata[15:1]; lane0上每个第一次采样的//数据位

signal0_cntrl0 <= rx_tdata[0]; lane0上每个第一个采样的//控制位

//通道1

signal1_sampl1 <= rx_tdata[63:49]; lane1上每秒采样的//数据位

signal1_cntrl1 <= rx_tdata[48]; lane1上每秒采样的//控制位

signal1_sampl0 <= rx_tdata[47:33]; lane1上每个第一个样本的//数据位

signal1_cntrl0 <= rx_tdata[32]; lane1上每个第一个采样的//控制位

//通道2

signal2_sampl1 <= rx_tdata[95:81]; lane2上每秒采样的//数据位

signal2_cntrl1 <= rx_tdata[80]; lane2上每秒采样的//控制位

signal2_sampl0 <= rx_tdata[79:65]; lane2上每个第一个采样的//数据位

signal2_cntrl0 <= rx_tdata[64]; lane2上每个第一个采样的//控制位

//通道3

signal3_sampl1 <= rx_tdata[127:113]; lane3上每秒采样的//数据位

signal3_cntrl1 <= rx_tdata[112]; lane3上每秒采样的//控制位

signal3_sampl0 <= rx_tdata[111:97]; lane3上每个第一个采样的//数据位

signal3_cntrl0 <= rx_tdata[96]; lane3上每个第一个采样的//控制位

配置方面的任何帮助和/或我必须如何使用来自 Rx_data 的 IQ 样本来获取斜坡或 Sinewave 的原始数据都将是很好的。

提前感谢。

最棒的

迟浩田