您好!

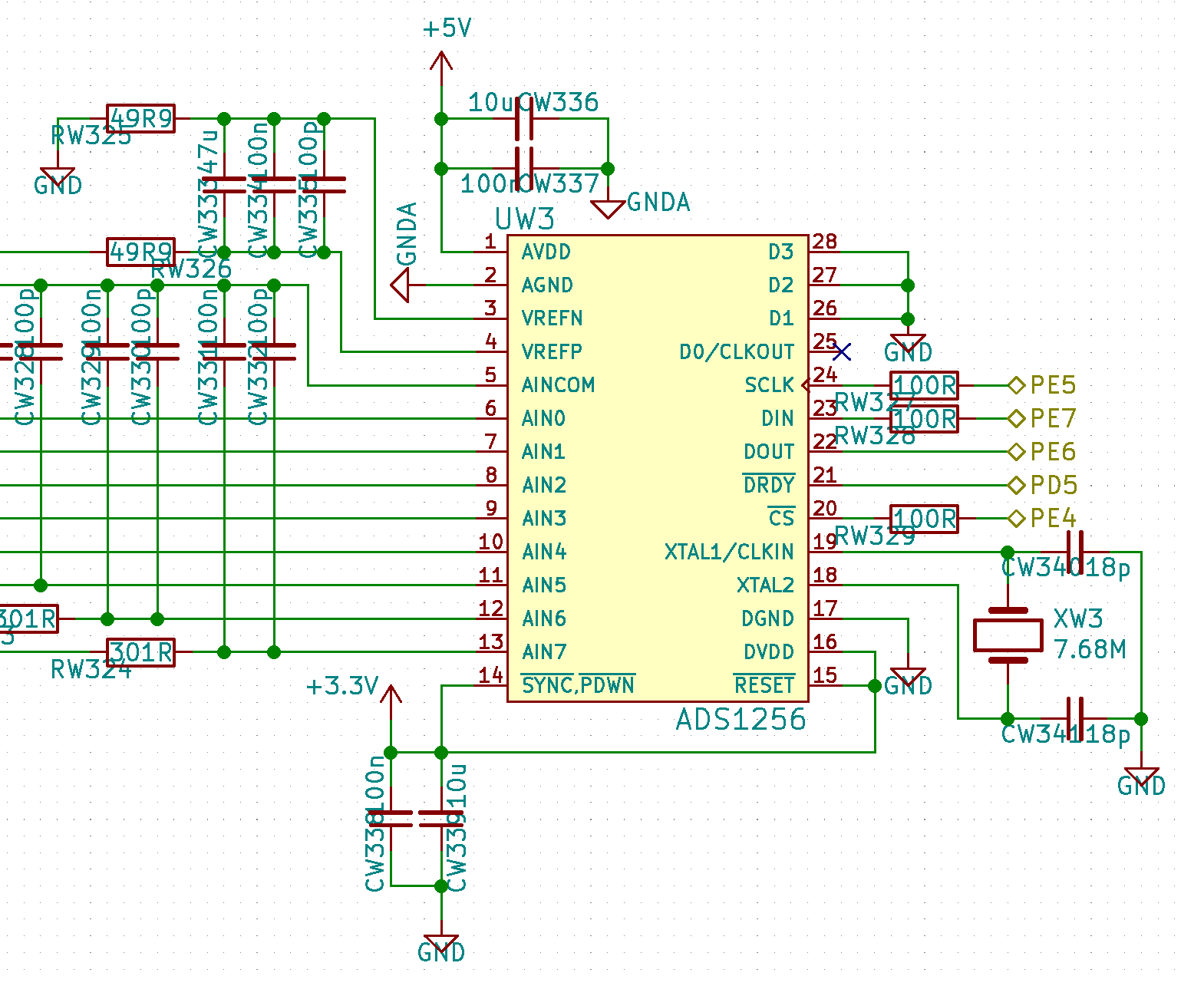

我尝试与 ADS1256通信、但无法将 DRDY 置为低电平。 SPI 端口工作正常、因为我已经对其进行了色谱、并在示波器上看到 OK 信号。 我使用 SPI 模式1、大约1MHz 的 CLK 信号 随附我正在使用的代码。 它基于此论坛中提供的答案来查看您是否正在与 DE ADC 通信( e2e.ti.com/.../154300 )

SPI_MasterSSLow (spiMasterE.port、PIN4_BM);//将 CS 设置为 low _delay_us (0.5);//在数据表中,它的 T3 = 0,但每个人都建议引入一个短延迟 SPI_MasterTransceiveByte (&spiMasterE、ADS_CMD_STANDBY);//发送备用命令 _delwake_ms (0xSPI_MasterByte ) ;/Spi_TransceiveByte;/Spi_Transceedeon_D&d&doweMasterByteD/ Spi_DP_D&d_D&d_D&d&d&d&d&d&d&dspiMasterByteMasterByteSpi_d&d&d&d&d&d&d&d&d&d&d&d&d&d& //发送 WREG DRATE SPI_MasterTransceiveByte (&spiMasterE、0); //发送以仅写入1字节 SPI_MasterTransceiveByte (&spiMasterE、ADS_DR_30000); //发送数据速率30000 SPI_MasterTransceiveByte (&spiMasterE、ADS_CMD_SYNC); //同步