您好!

我们在同步从模式下使用两个 ADS131A04作为链、禁用 CRC、24位、关闭汉明码以及自由运行的 SCLK (7.8125MHz)。

我们使用内部基准 AVSS -2.5 AVDD 2.5 IOVDD 3.3

经测试的输入信号为1kHz 正弦波、具有2~3V pk-pk (0至2~3)

我们有与 ADS131A04EVM 中相同的原理图。

启用 ADC 后、我们不会获取任何数据、我们执行了数据表中的大多数配置、因此我们不确定是否错过了一个步骤。

完成了以下寄存器配置:

A_SYS_CFG (0Bh)- 68h

D_SYS_CFG (0Ch)-默认值

CLK1 (0Dh)- 82H

CLK2 (0Eh)-默认值

ADC_ENA (0Fh)- 0Fh

其余用户配置的寄存器保留为默认值。

这是我们为启用 ADC 所执行的以下命令、这些命令一个接一个地完成、并且在一次性完成所有命令之前、已使用数据表检查了它们的响应。

解锁

WREG 0D 82

WREG 0B 68

WREG 0F 0F

唤醒

锁定

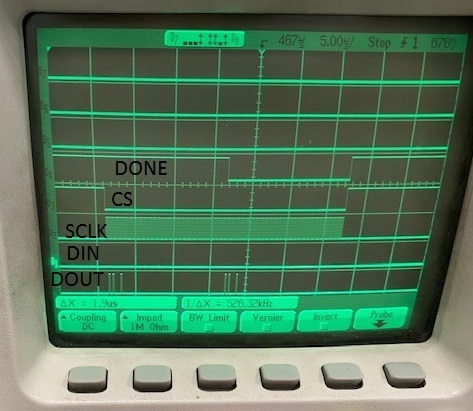

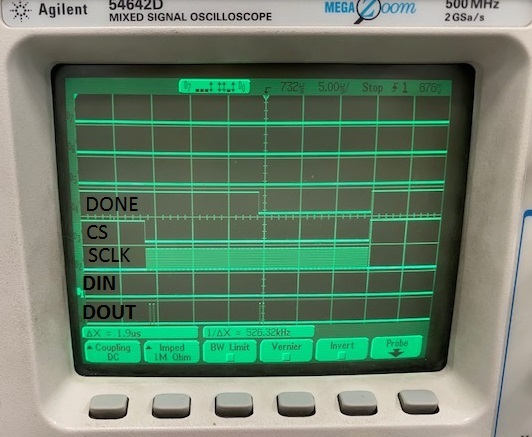

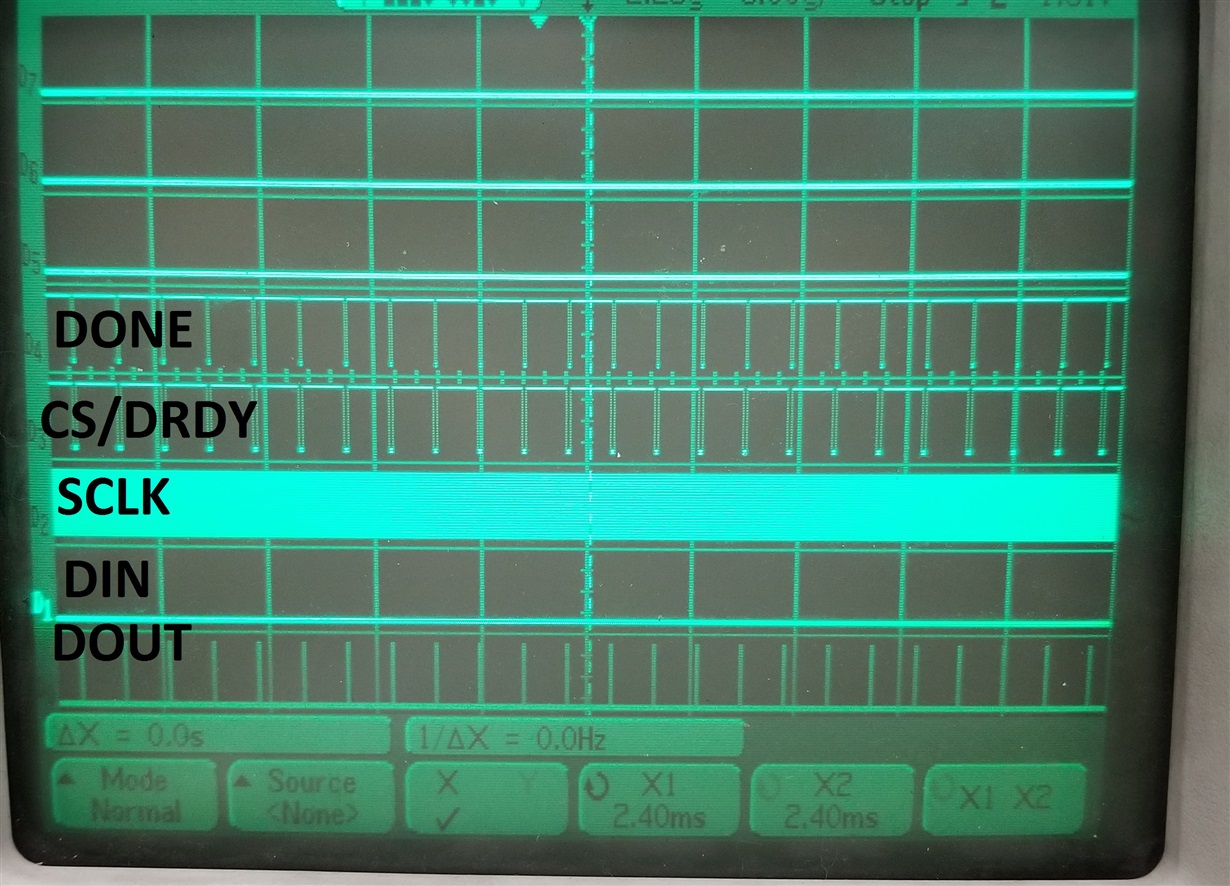

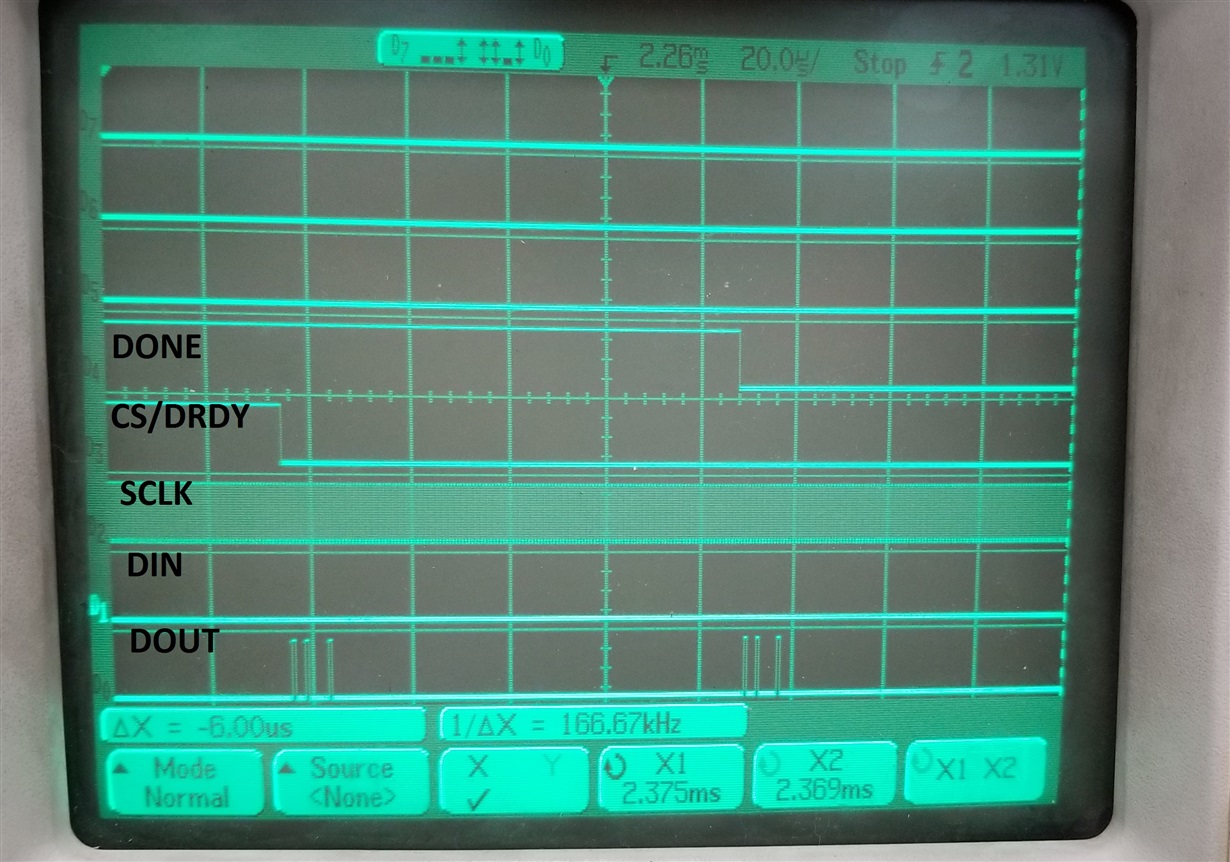

以下图片显示了我们从示波器中得到的结果、我们遇到了一些/DRDY 故障、但没有频繁发生、这就是我们不确定这是否是唯一的问题的原因

这就是我们得到的结果:

我们检查了所有寄存器、以确保正确配置它们、并且所有寄存器都返回了所需的结果。 DONE 和 CS//DRDY 频率均匹配。

您是否知道问题可能是什么? 我们以前遇到了一个问题、因为没有从第二个器件获得响应、但在第二个器件的 DONE 变为低电平后、通过发送命令来解决该问题。