请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC12DL3200EVM 主题中讨论的其他器件:LMK04828、 TSW14DL3200EVM、

您好!

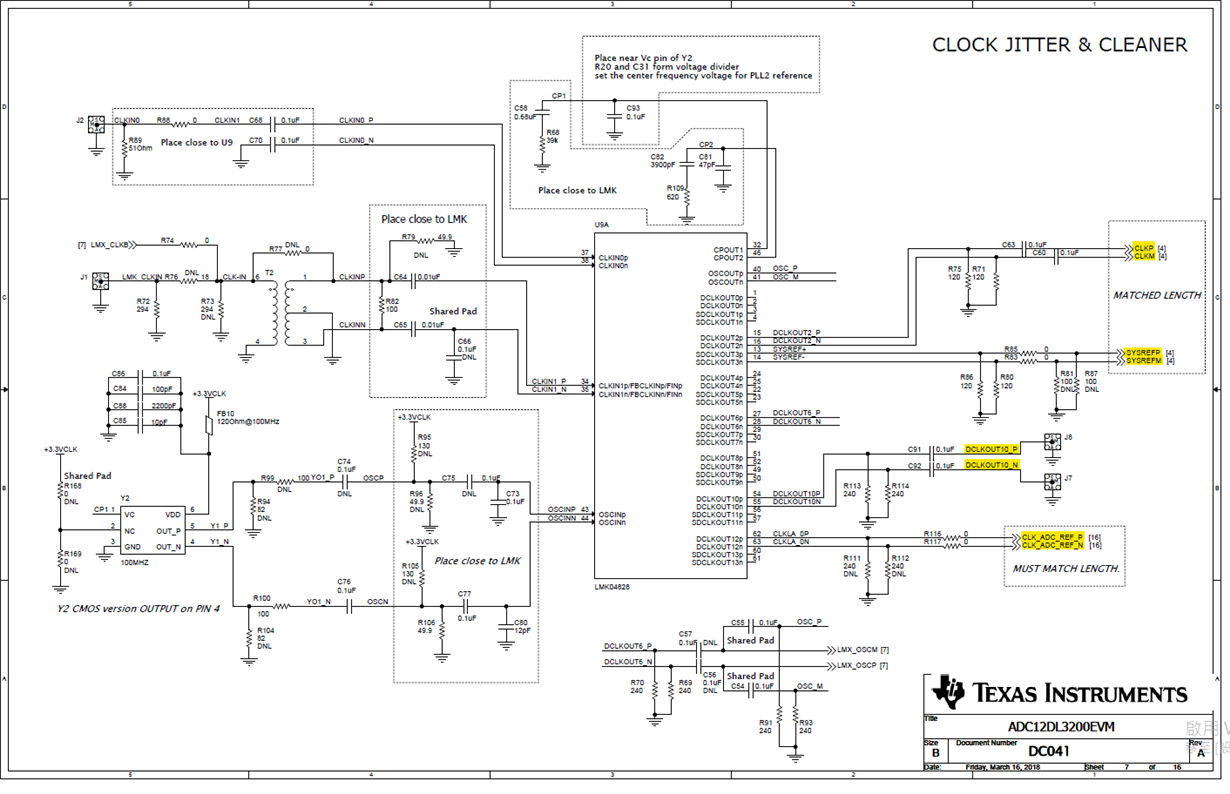

下图是原理图文件中的 LMK04828。 在外部时钟模式下运行时、我发现实际上没有使用 LMK04828的输出。 未使用 CLKP/M。 7.3.4.3.1 ~ 7.3.4.3.2中描述的 SYSREF 校准未被执行、因此没有从 SYSREFP/M 发出信号 DCLKOUT10_P/N 和 CLK_ADC_REF_P/N 也未在参考设计中使用。 在这种情况下、LMK04828是否不是必需的?

此致、

阿尔茨