主题中讨论的其他器件:THS4561、 THS4531、

大家好、

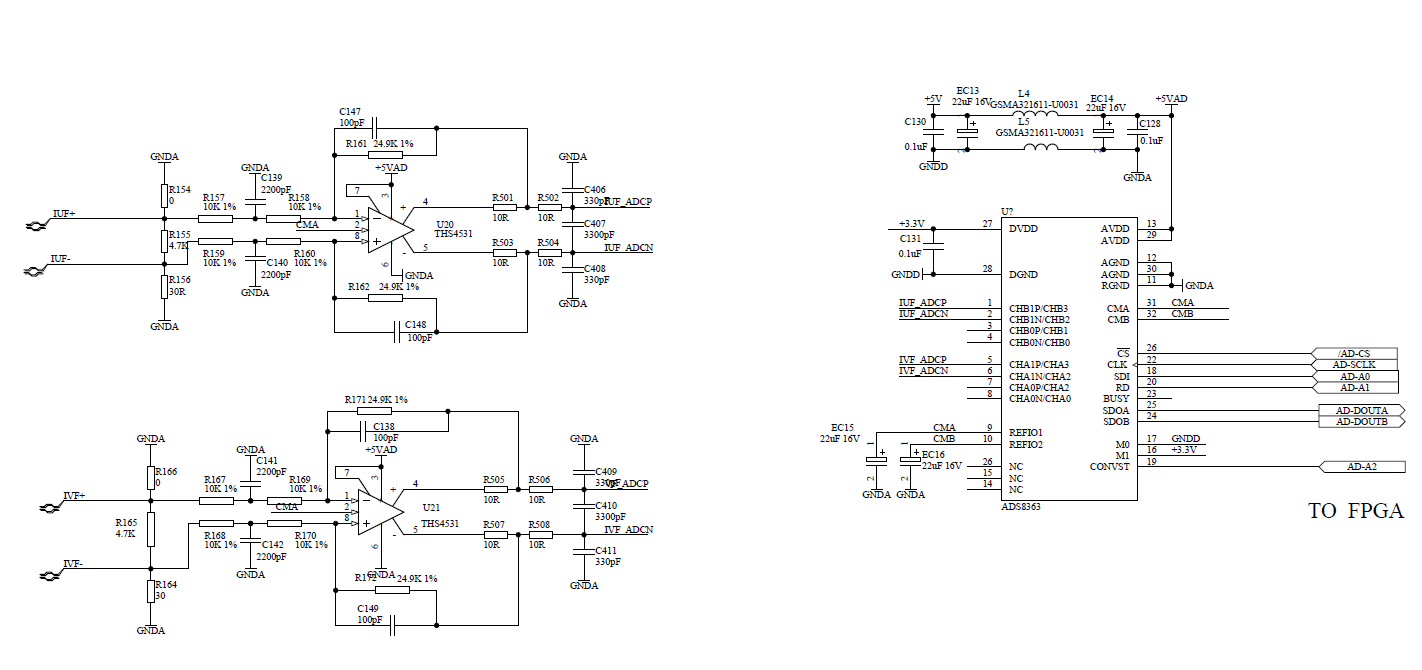

这是我的客户设计。 您可以帮您提供任何意见吗? 下面是我找到的内容、

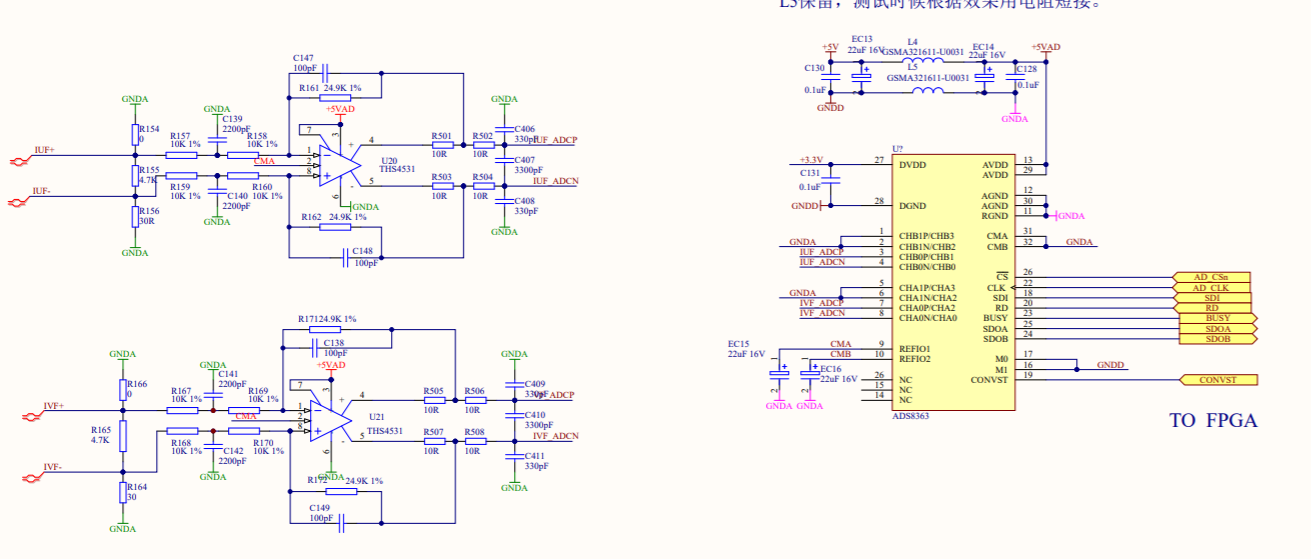

1.将 CMA/CMB 引脚保持断开状态、因为它是全差动输入用例;

2.拆除 R154 R155 R156 C139 C140 C147 C148 C406 C408;

3.对于16位应用、请选择偏移较小的 THS4561;

FDA 的输入信号为2.5V 共模电压、摆幅为+-2V。 ADS8363的差分+-2.5V 输出摆幅的增益为1.25V/V。 我想将 THS4531的 OCM 设置为 ADS8363的2.5Vref。 FDA 可由5V 单电源供电。

这是一个双通道同步采样。 我能否使用 REFIO1同时为放大器的 ADC 和 OCM 供电? 我认为缓冲 REFIO1可以做到这一点、单个基准会引入更高的精度。

BTW、我在数据表中找不到 ENOB 数据。

谢谢。