主题中讨论的其他器件: ADC31JB68EVM、 TSW14J10EVM、 DAC38J84、 ADS54J69EVM

尊敬的 TI 支持者:

我正在使用 DAC38J84EVM + TSW14J10 + ZCU106 (带 ZCU7EV 的 Xilinx EV 电路板)进行测试。

我已将"TI_HSDC_Pro_Reference_Design_V2.8"修改为随附的 zip 文件、用于 Vivado 2019.2和 ZCU106板。

我在脚本中修改并添加了3个板设置、如下所示。

- ZCU106_1P:具有 JESD204B 1对(2条通道)链路、用于 ADC31JB68EVM。 成功了。

- ZCU106_2P:具有 JESD204B 2对(4通道)链路、用于 DAC38J84EVM。 SYNC 为低电平。 发送数据卡在“WriteDrpReg()”函数处。

- ZCU106_4P:具有 JESD204B 4对(8通道)链路、用于 DAC38J84EVM。 SYNC 为低电平。

我的目标设置为 ZCU106_2P。

ZCU106_4P 仅用于测试。

###对于这两种设置、SYNC 均为低电平。

我已经使用 D3 LED 进行了检查、该 LED 连接了 FPGA 的 SYNC_LED 输出。

此外、我还使用警报测试点和 DTest 设置(0100、SYNC、CONFIG27)检查了它

我已对 TSW14J10EVM 用户指南进行以下修改。

由于 ZCU106在用于 TX_syncp/TX_syncn 的 FMC 连接器中也没有连接、如 ZC706。

ZC706开发平台在 FMC 连接器引脚 F10和 F11上没有布线、

通常用于 JESD204B DAC 同步差分信号。 为了适应这种情况、

TSW14J10EVM 可通过以下方式将 SYNC 信号移至 FMC 引脚 H19和 H20

电阻器变化:

1.拆下 R143、R145。

2.为 R142、R144、R146和 R149安装0 Ω 电阻器。

这些电阻器都位于 TSW14J10EVM 底部靠近 FMC 连接器的位置。

### ZCU106_2P 设置在发送数据时卡在“WriteDrpReg ()”函数中。

发送数据时,ZCU106_4P 设置不会卡在 WriteDrpReg 函数中。

我已附加了来自 Microblaze 固件的两种设置的调试消息。

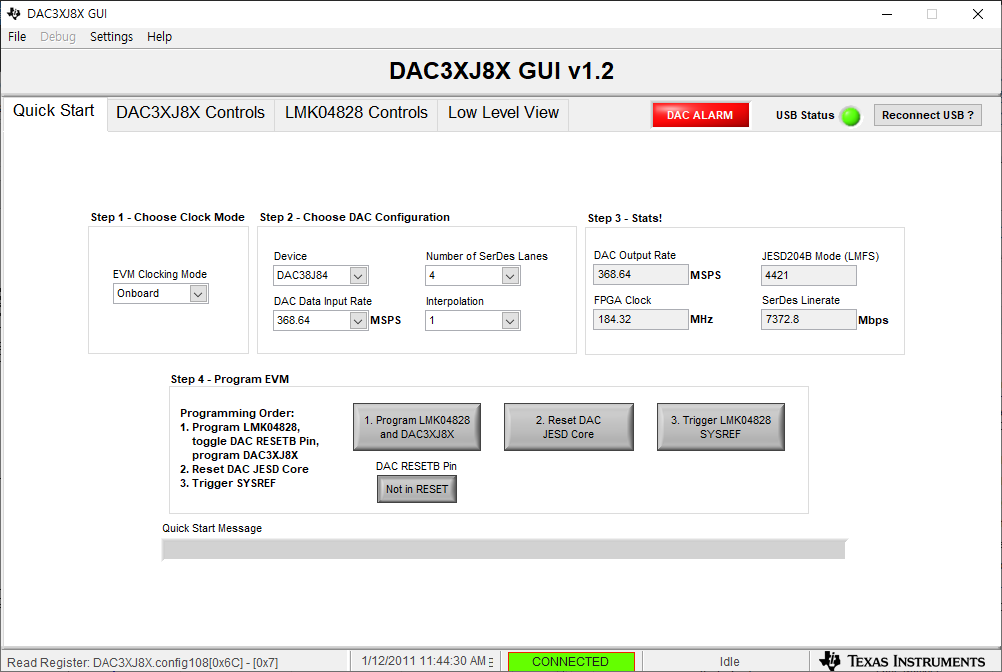

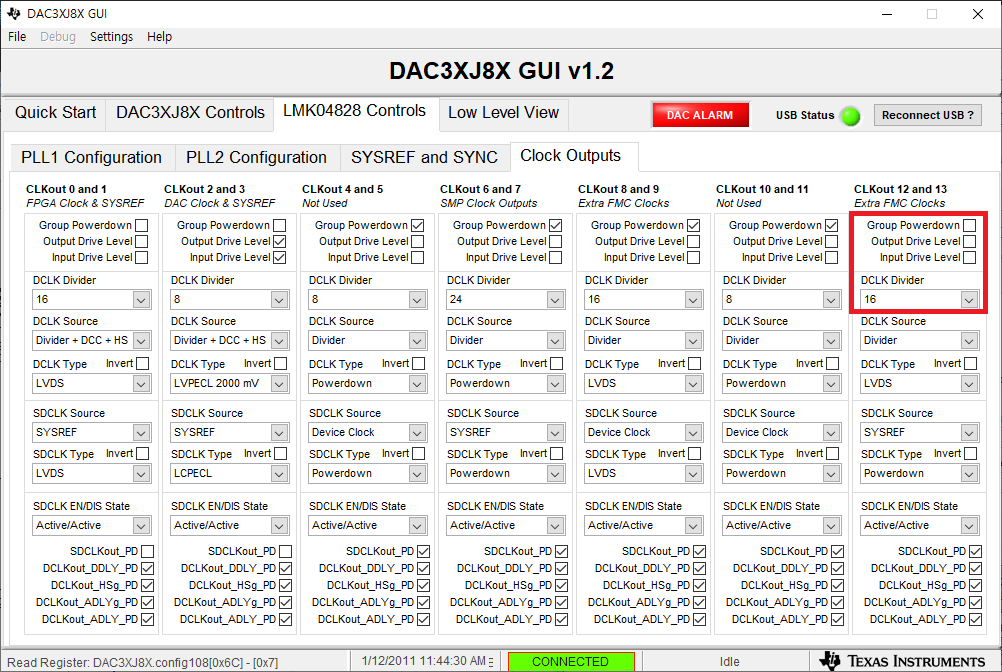

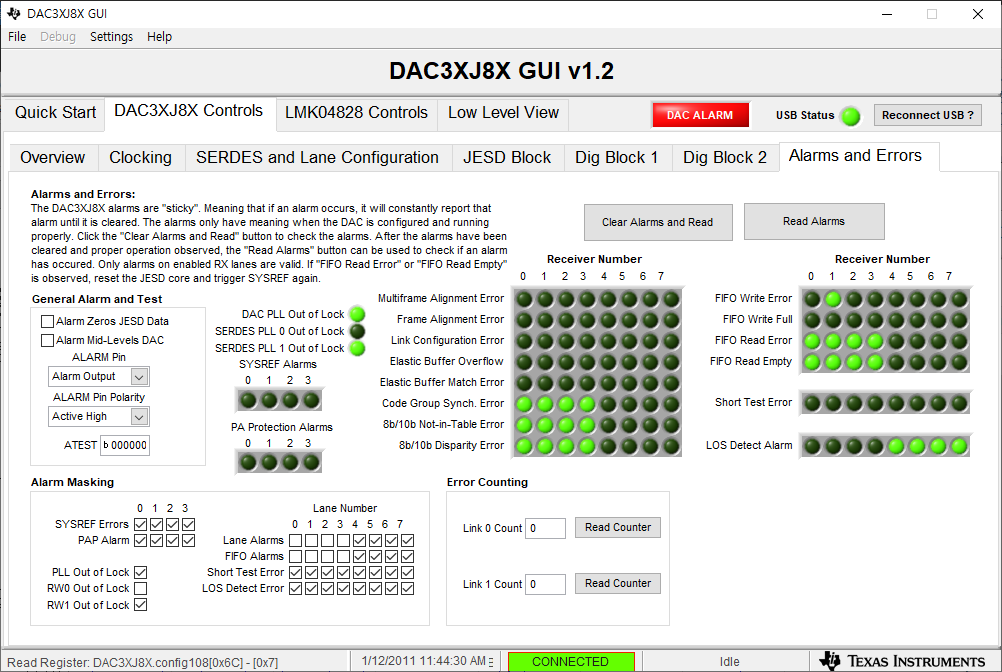

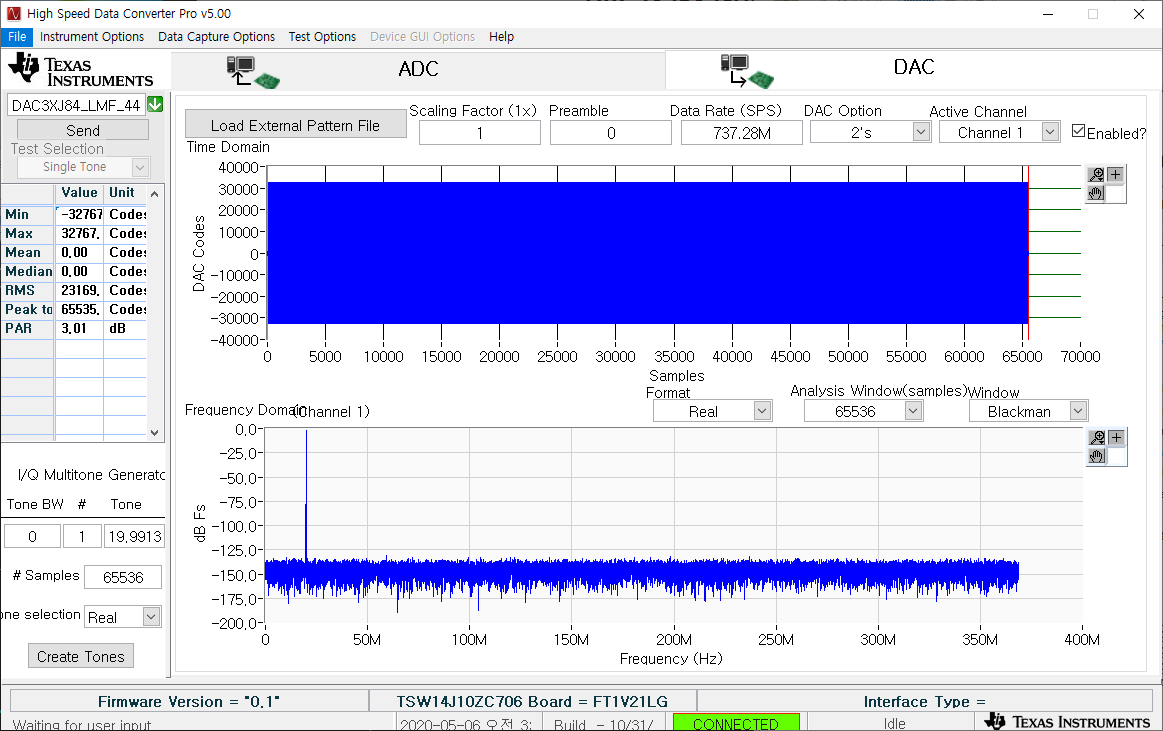

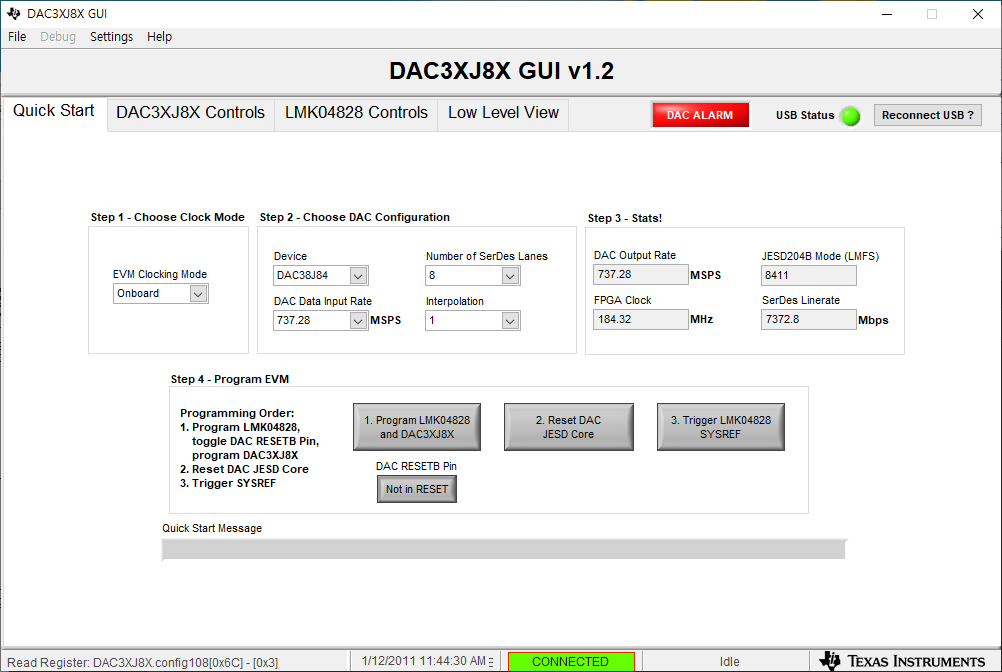

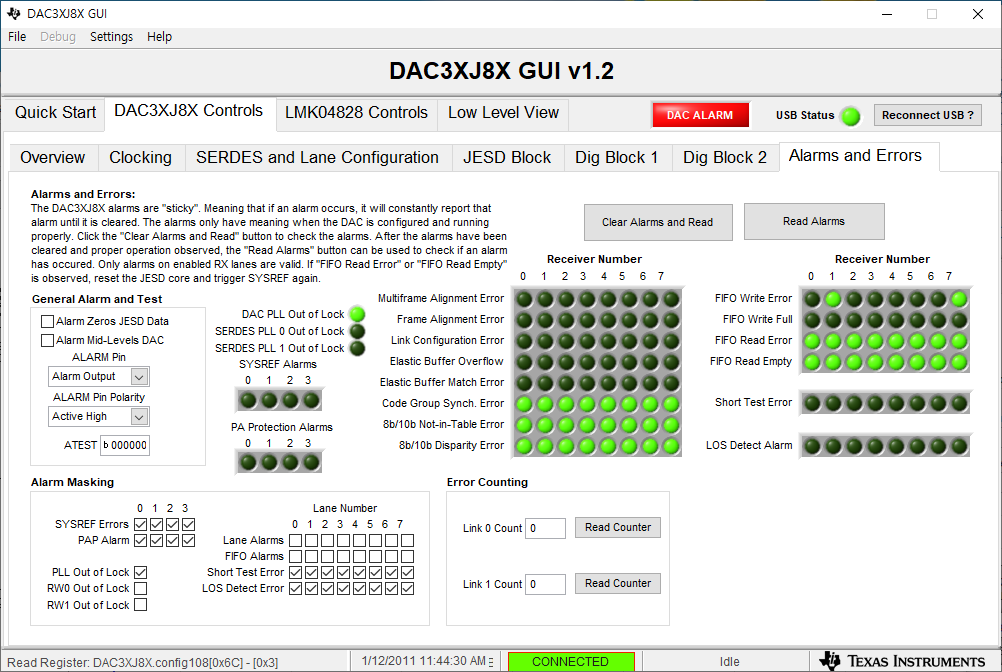

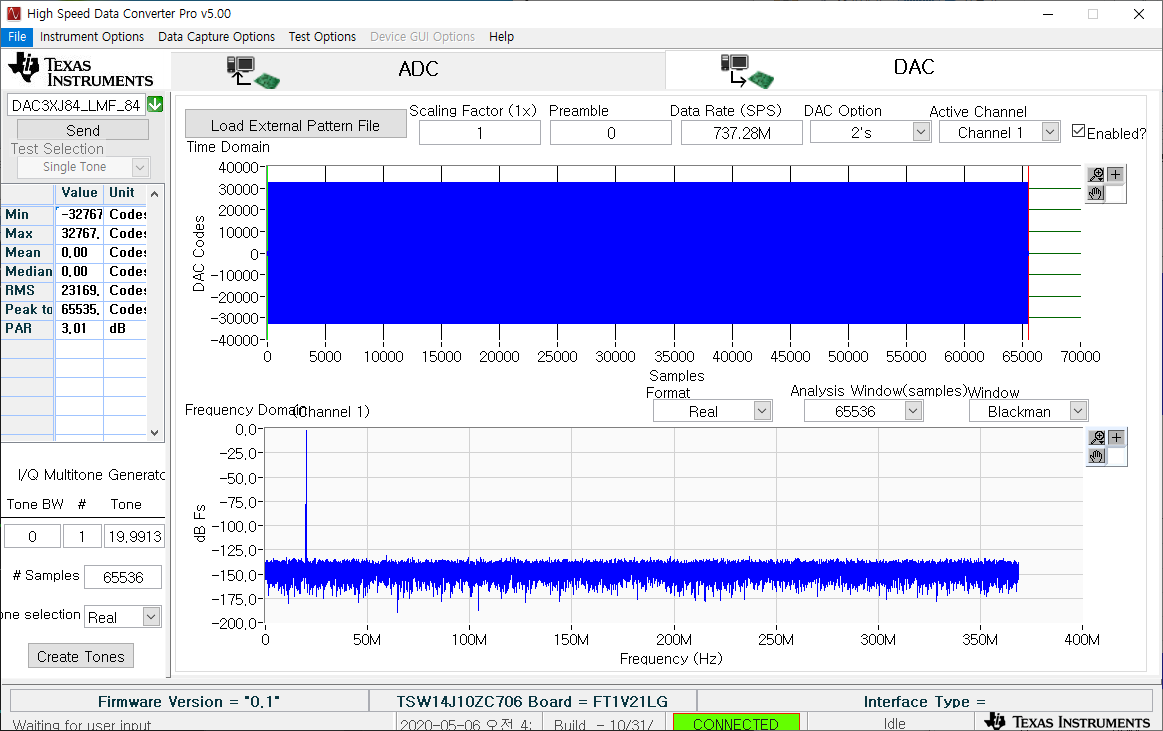

Belowes 包括快速启动、LM04828时钟输出设置以及从 HSDC 专业版发送数据后针对 ZCU106_2P 设置的警报。

Belowes 是针对 ZCU106_4P 从 HSDC 专业版发送数据后的快速启动、LM04828时钟输出设置和警报。

时钟输出设置与 ZCU106_2P 相同。

我还附加了来自 Microblaze 固件的调试消息。

我分析了这些信息,但找不到问题的原因。

请检查我的修改和 GUI 设置。

e2e.ti.com/.../ZCU106_5F00_2P_5F00_Debug_5F00_Messages.txt

e2e.ti.com/.../ZCU106_5F00_4P_5F00_Debug_5F00_Messages.txt

e2e.ti.com/.../TI_5F00_JESD204_5F00_Ref_5F00_ZCU106_5F00_2020_2D00_05_2D00_06.zip