Other Parts Discussed in Thread: LMK04828

当我使用 DCLKout0和 SDCLKout1作为输出时、请在 TICS Pro 中选择 SDCLKout1作为器件时钟、两个通道的输出波形具有269ps 的延迟、为什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我不希望器件输出端出现如此大的偏斜变化。 您是否在 SMA 上使用 LMK04828EVM 进行测量?

您是否将完全相同的电缆长度从 SMA 连接到示波器? 假设电缆的传播速度为65%、则长度误差为5.24cm (长度误差= 0.65 *(3e10cm/s)* 269ps)、将导致大约269ps 的时序误差。

您是否在示波器中打开了任何偏斜?

如果您将电缆交换到 PCB 上的连接位置、偏斜是否变为-269ps?

如果您使用的是探头、如果您探测到完全相同的点、那么偏斜是否= 0ps?

请共享您已编程的配置文件。

谢谢。

73、

Timothy

您好!

Timothy。

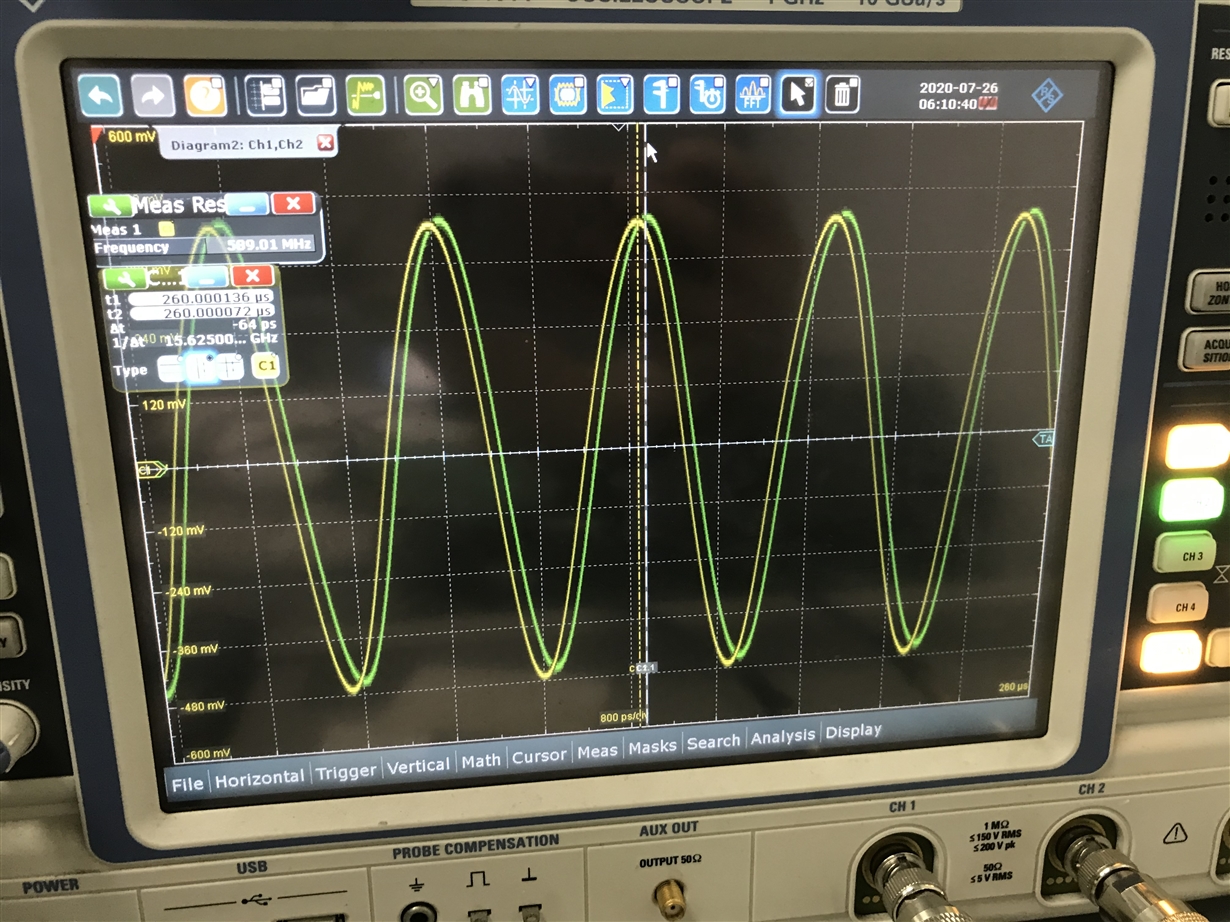

我仍然有问题。 当我使用 DCLKout0和 SDCLKout1作为输出时、选择 SDCLKout1作为器件时钟、在更改分频器的值后按工具栏顶部的同步分频器、但延迟没有改变、 当我将分频器的值更改为3、4和5时、两个输出的信号延迟为120ps、260ps 和60ps、这是不同的、为什么?

当我使用 SDCLKout1作为器件时钟时、能否单独更改 SDCLKout1的延迟以与 DCLKout0保持一致? 我如何?

大家好、

第二个想法是、同步不应影响 DCLKout0和 SDCLKout0之间的相位、因为两个输出都以器件时钟模式运行、因为它们由同一个分频器供源、并且除了通过更改 DCLKout0_POL 和 SDCLKout1_POL 位之外、它们不能在它们之间进行单独调整。 不同的输出格式可能会有小影响、但我不希望它针对不同的分频而改变。

您能否共享配置的已保存.TCS 文件?

同样、如上所述、我不认为这对您的配置而言是个问题、但对于 您希望确定性相位的任何输出、请取消选中 DDLY_PD。 时钟同步分频器应取消选中此位。

73、

Timothy

您好!

感谢您的参与。

这里是我 的.TCS 文件和 示波器中的不同延迟信号。 示波器的两个通道的连接不同、这可能会导致一些延迟 、但我认为当我更改分频器的值时、DCLKout0和 SDCLKout0之间的延迟应该不变。 我不知道为什么我会有不同的延迟。

e2e.ti.com/.../1667.3divider.tcse2e.ti.com/.../4divider.tcse2e.ti.com/.../5divider.tcs

您好!

我今天测试了这个、没有测量如此大的差异。 所有除法设置都在20ps 范围内。

我假设您在示波器上使用50欧姆端接、并且该对的未连接输出端接50欧姆?

我会使用完全相同长度的电缆。 我知道 LMK04828 EVM 在 SMA 连接器输出端存在一些阻抗不匹配、差分布线分离处的薄布线以及 SMA 的厚垫、我想知道这是否会由于您的电缆长度不同而增加测量误差。

-您能用完全相同长度的电缆进行测试吗?

73、

Timothy