主题中讨论的其他器件: LMK04828

大家好、

这是通过以下 URL 重新发布到 DAC 论坛的内容。

此外、问题已更新。

e2e.ti.com/.../3409946

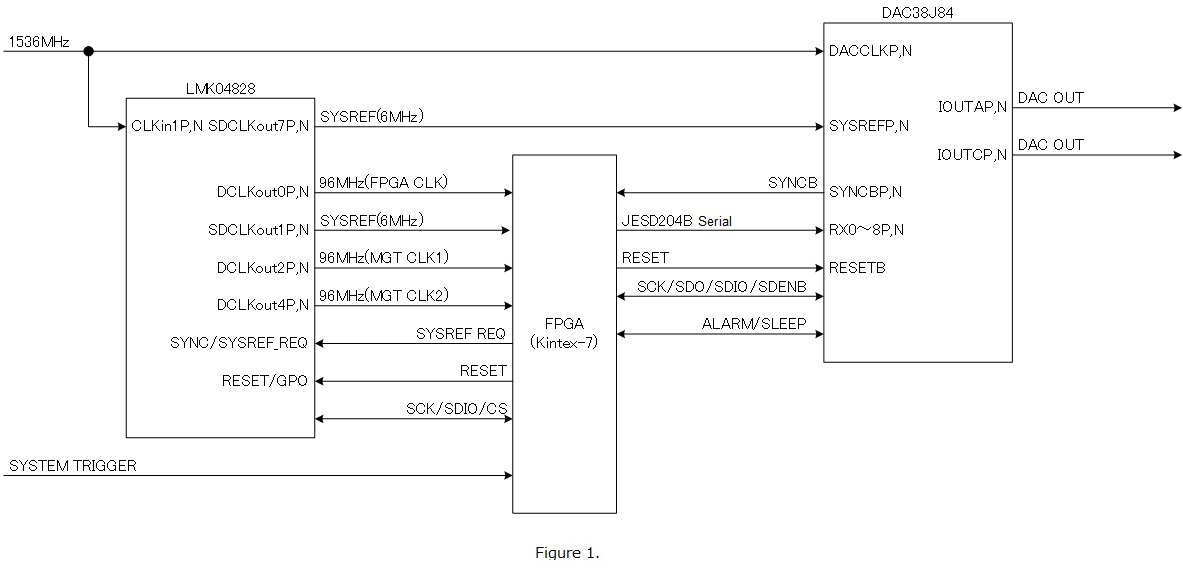

我们目前使用 Xilinx FPGA Kintex-7和 Xilinx JESD204 IP 内核通过 TI DAC (DAC38J84)输出模拟信号。

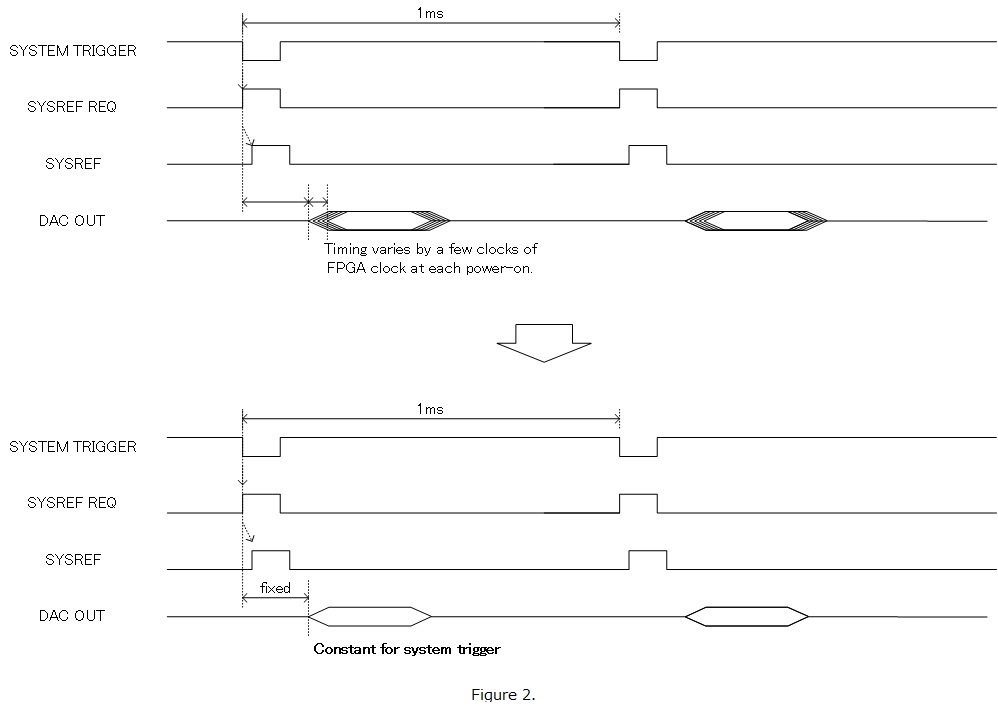

例如、FPGA 每1ms 接收一次触发信号、并且需要在该时间输出模拟信号、但每次打开电源时、FPGA 时钟中的几个时钟之间的模拟输出时序会波动。

但是、模拟输出时序在每次电源启动时的几个时钟之间变化、我们希望在相同的时序输出模拟信号。

我们在子类1中使用 JESD204B、但我们在子类1方面没有太多经验、也不了解 JESD204B 的操作、因此我们想向您询问以下内容

"运行条件"

DAC 为 DAC38J84、LMK04828用于时钟和 SYSREF 生成。 (图1)

FPGA 是一款具有 JESD204子类1 IP 内核的 Xilinx Kintex-7。

"问题"

Q1)例如、如果寄存器固定为特定设置、DAC 中的内部延迟是恒定的还是波动的?

例如、DAC 中特定寄存器设置的内部延迟是恒定的、还是存在变化的因素?

它可能与 FPGA 的 IP 内核有关、但我想知道是否可以在每次启动时输出模拟信号而不会出现任何触发时序波动。

Q2) SYSREF 由系统触发器生成、并尝试模拟输出。 (图2)

加电或复位时、SYSREF 时序和模拟输出时序波动。

(我不确定、但它似乎在1个多帧之间波动。)

我提到过以下论坛和其他论坛、但我没有看到任何变化。

您有什么解决方案吗?

由于时钟、SYSREF 和触发器是同步的并且没有显示任何变化、我认为还有另一个问题。

e2e.ti.com/.../ f/73/p/793625/2940186?tisearch=e2e-sitesearch&keymatch=DAC38J84#2940186

Q3)我需要在每次触发时序上使用 SYSREF 来复位 NCO。

但是、如果您看看模拟输出、相位会每次发生变化。

如果您看看复位时看到的振铃、它会在大约5ns 的周期(192MHz?)内发生变化 在1个多帧中、SYSREF 输出时序和触发周期是正常的。

您能找出此问题的原因吗?

Q4)"链路配置错误"和"Read_empty"标志。 被写入寄存器中。

这是否与时序变化有关?

目前、通过屏蔽进行连接。

此外、"链路配置错误"到底是什么?这意味着什么?

我们将向您发送 DAC 设置信息和寄存器配置文件。

LMFS 设置:4421

内插率:8.

RBD 设置:31

K 设置:32

NCO 设置:32

0x3555_55555_5555 (DACAB 路径)

0x2000_0000_0000 (DACCD 路径)

e2e.ti.com/.../dac38j84_5F00_config.xlsx

如果您还有其他需要注意的问题(设置、使用等)、如果您能给我一些建议、我将不胜感激。

此致、

T.Karita