工具/软件:Code Composer Studio

您好!

使用 ads1292时遇到问题。

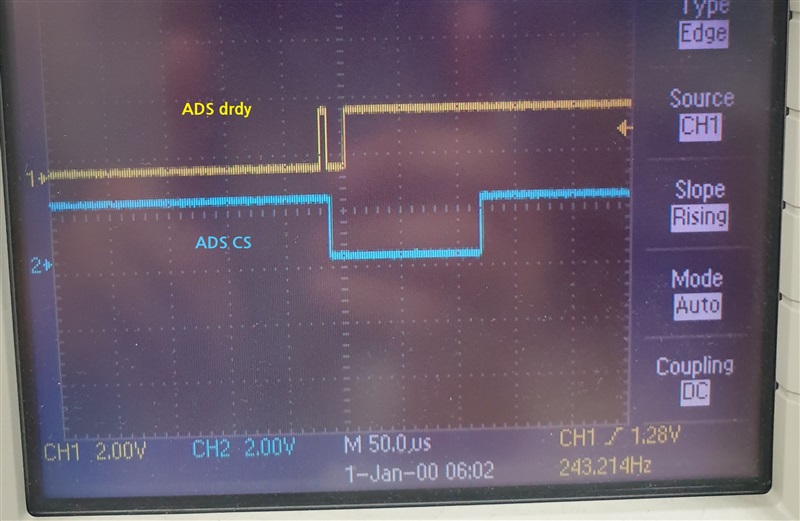

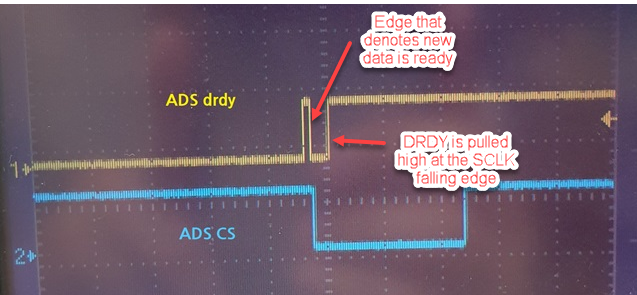

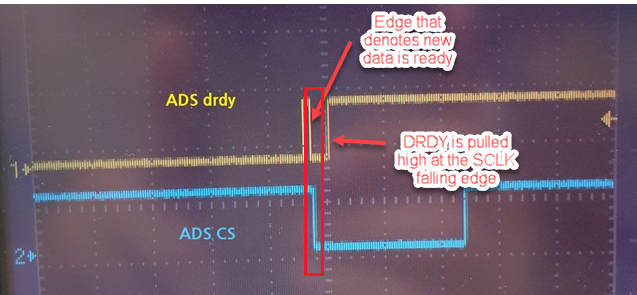

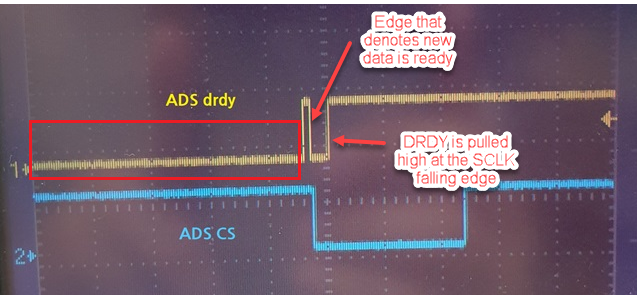

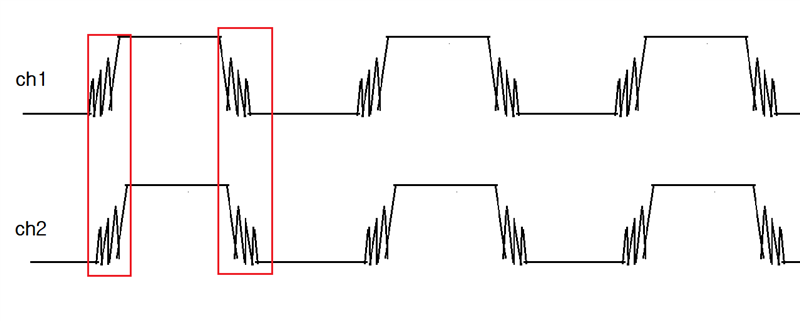

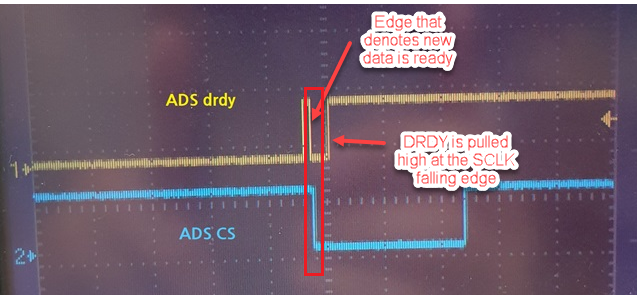

当我使用连续模式读取样本时、ADS 状态的 drdy 引脚异常。

(中断边沿从低到高:上升边沿)

有人知道这些问题吗?

这是我的代码。

int main (void) { WDT_A_HOLD (WDT_A_base); INIT_CS (); INIT_GPIO (); //GPIO_setPeripheralModuleFunctionOutputPin (GPIO_PORT_PJ、GPIO_PIN2 | GPIO_PIN1 | GPIO_PIN0、GPIO_primary_module_function); init_mainOperation (_interrupt );_main_main_main_main (); initUserPort(); setPowerEnPin (true); initADS1292(); hal_ads_start(); read_start=1; while (1) { mainOperation (); if (ads_read_flag) { hal_ads_read_sample (ads_buff); ads_read_flag = 0; } #pragma vector=Port1_vector __interrupt void P1_ISR (void) { switch (__even_in_range (P1IV、P1IV_P1IV_P1PI_break) ;p1p1p1p1g1_if = 1;p1p1pif_break = p1p1p1p1p1;p1p1p1p1pif_g4;p1p1p1p1p1pif_rid = p1

- ADS1292 SCLK:1MHz

- ADS1292 CLK:MSP430 2MHz

这是 ads1292的寄存器设置。

0x01,//CONFIG1:单次触发模式 为4kSPS 0xF3,//CONFIG2:启用导联脱落比较器,启用基准缓冲器,参考4V 0x10,//LOFF 0x65,//Channel1 //断电 0x65,//Channel2 //gain12 0x25,//RLD_SENS 0x02_SENFF ,0x40/ STAT_S //RESP1 0x03、//RESP2 0x03 // GPIO

谢谢。

此致、

Youngjun