您好!

TLC2558数据表规定、当 fs=1时、从 SCLK 上升沿到 SDO 有效、TD (CLK-Dov)。

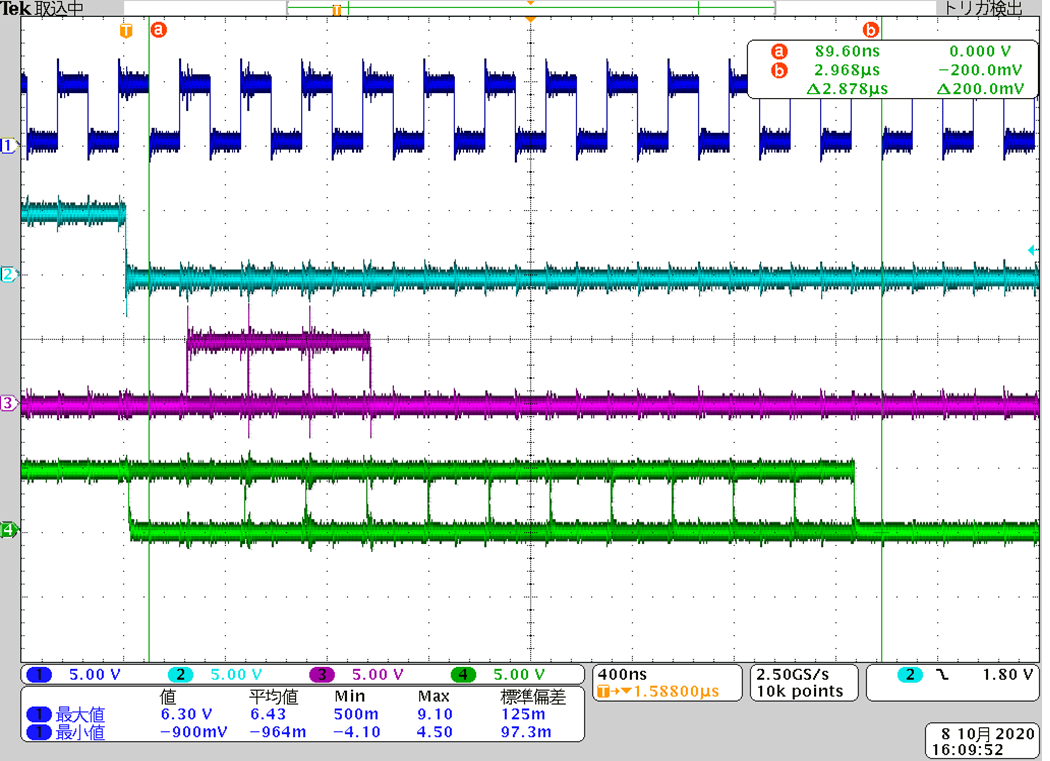

但是、我的客户在 fs=1时捕获了 SPI 波形、如下所示。 (CH1=SCLK、Ch2=CS、Ch3=SDI、Ch4=SDO)

SDO 似乎在 SCLK 下降边沿上有效、而不是数据表中指定的上升边沿。

数据表是否错误?

此致、

希拉诺

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tom、

感谢您的回答。

FS 输入始终为高电平、静态。

我的客户使用随附的.xlsx 文件中的10MHz SCLK 重新捕获波形。

SIO 在 SCLK 上升沿发生变化。

e2e.ti.com/.../EAM1_5F00_TLC2558.xlsx

此致、

希拉诺