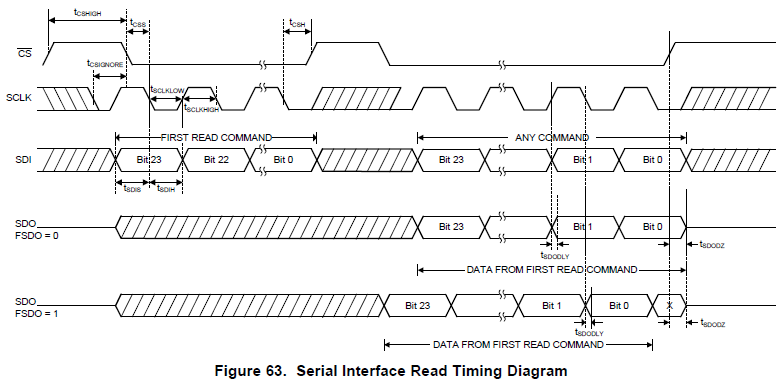

SBAS871C (2017年8月)数据表说明了图63中的读取时序、但未能通过 CS、SCLK 和读取位23的协调正确说明读取数据事务的开始。 在命令/数据事务对之间没有正确地说明 SCLK;我假设当 CS 在命令和数据事务中变为低电平时 SCLK 应该为高电平、但这并不清楚。 命令和数据之间没有说明 SDO 三态。 在 CS 高电平期间、SDO 是否会保持驱动? 如果 FDSO=1、读取位23是否显示(还是保持?) 在对命令位23进行采样的第一个下降时钟之后、CS 变为低电平并更改为位22?

上一个论坛问题 DAC80504的图示:与 DAC80504连接时出现的问题 显示了更完整的时序图、但所示参数不属于 DAC80504寄存器映射。

以上两个图中的一个是否对应于 DAC80504的运行? DAC80504上是否提供 CPOL 或 CPHA?

非常感谢您的任何见解。

JH