主题中讨论的其他器件:ADC12DJ3200

大家好、

另一位客户询问 ADC12DJ5200RF、很抱歉再次打扰您。

客户问题描述如下:

ADC 为 ADC12DJ5200RF 并配置为 JMOD1。 传输层代码是参照 ADC12DJ3200的示例项目编写的。 仔细检查后、未发现任何问题。

2. JTEST=Ramp 测试模式时,读出的数据正确,表示链路正确。

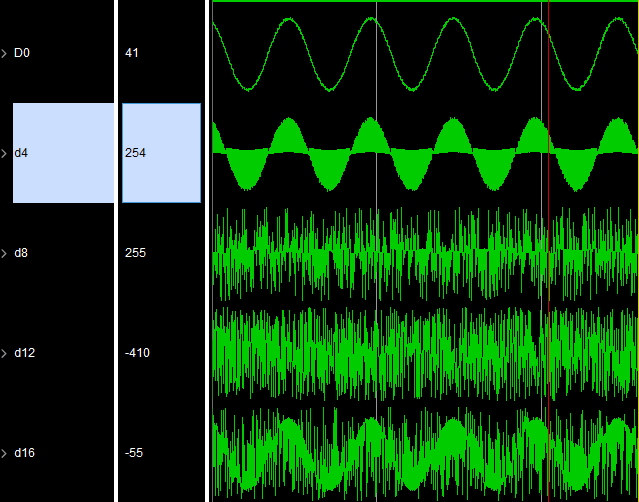

3.更改为 JTEST=nomal 模式后、发现传输层的输出波形只有一部分是正确的正弦波(输出为240位、分为20个通道* 12位)、其余的错误。 一些波形如下所示

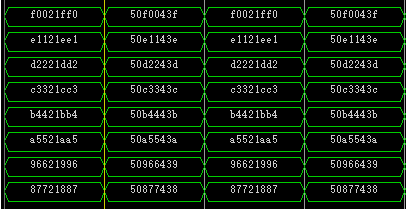

4.为了找出问题,我配置 JTEST=Transport Layer 测试模式,观察 lane0 ~ lane7接收到的数据,并查看测试数据是否错误。 它不同于表61中的说明。 数据表中 n '= 12、f = 8种模式(长度= 1帧)的短传输测试模式。 数据似乎放错了位置

如图所示:(从上到下、对应于表61的 DA0 ~ DA7)

传输层测试模式和斜坡测试模式之间的区别在于是否包含传输层。 这是否意味着传输层有问题? 可能的原因是什么?