请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS8698 降级器、

MCU 为:STM32F103、ADC:ADS8698。

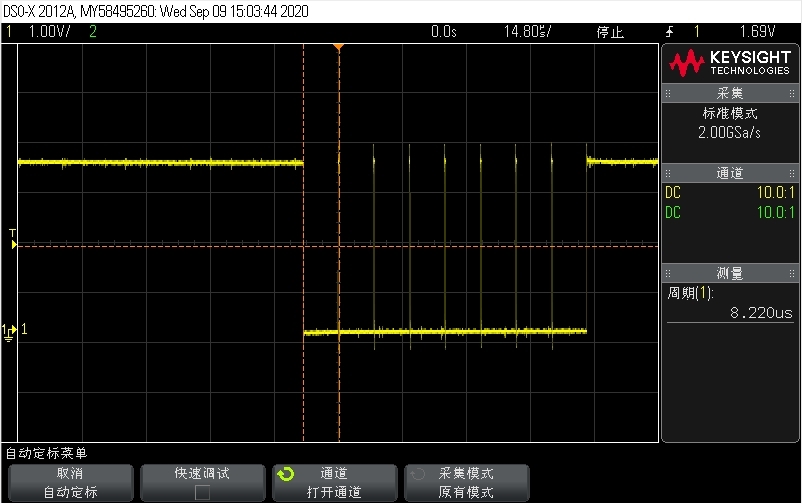

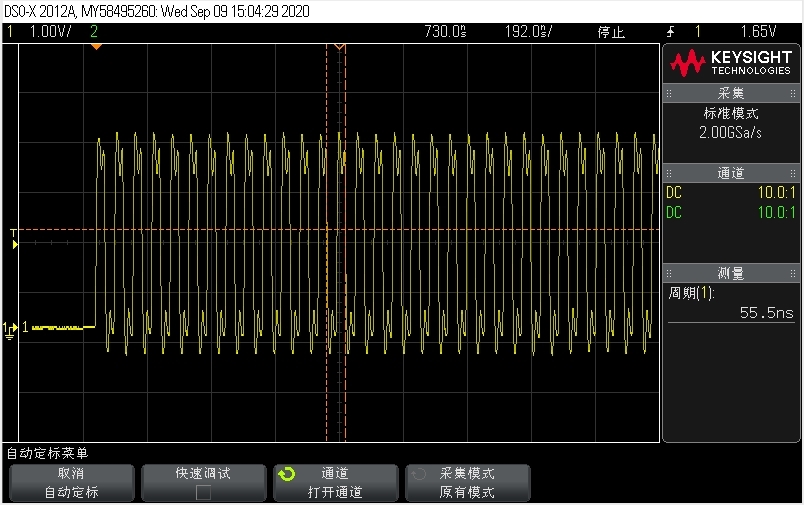

根据数据表、最大吞吐量为500kSPS、它们使用硬件 SPI、使用的 SCLK 为18MHz、每次发送和读取时、它们封装的函数为8位、因此总共16位被写入 ADC。 24位用于读取、CS 引脚由示波器测量。 CS 下拉和上拉的完成时间为:8.2us。 他们在这里使用8个通道,所以一轮使用的时间是:8.2*8=65.6us,那么总吞吐量是:1000000/65.6=15243,这相当于总吞吐量:15KSPS,所以他们不知道时间在哪里?

此致、

罗克苏