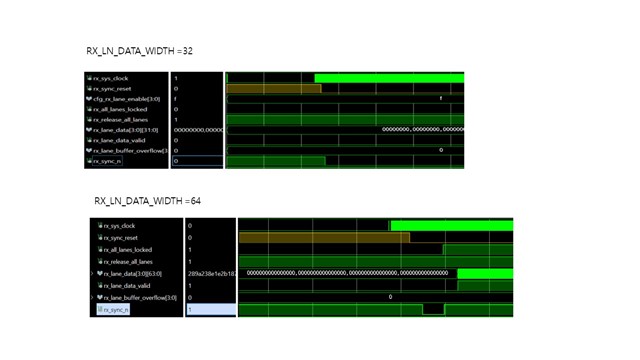

当我设置 RX_LN_DATA_width =64时、我可以成功接收 JESD204B IP 的64宽度用户流。

但是、当我设置 RX_LN_DATA_width =32时、我无法接收 JESD204B IP 的32宽度用户流。

我应该更改哪些参数?

<jesd_link_params.vh> `undef RX_LANE_DATA_WIDTH `define RX_LANE_DATA_WIDTH 32 <gth_8b10b_rxtx.sv> if (TX_BYTES_PER_LANE == 4 && RX_BYTES_PER_LANE == 4)