主题中讨论的其他部件:TMS320C5535、 ADS131A04EVM

我目前正在尝试从 ADS131A02DC 接收数据、但 DRDY 线路有问题。 我的硬件设置为 M0为高电平(异步中断模式)、M1为高电平(32位)、M2为低电平(禁用汉明)。 我成功地写入和读取了 ADC 寄存器、并读取了 STAT_M2寄存器、以验证我的硬件设置是否正确(正确)。

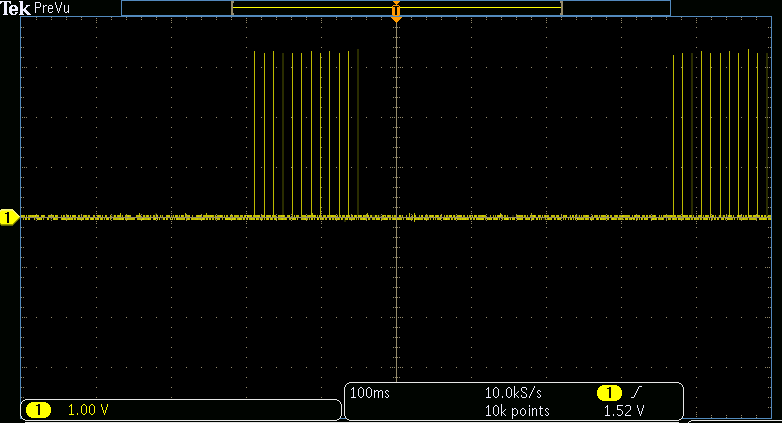

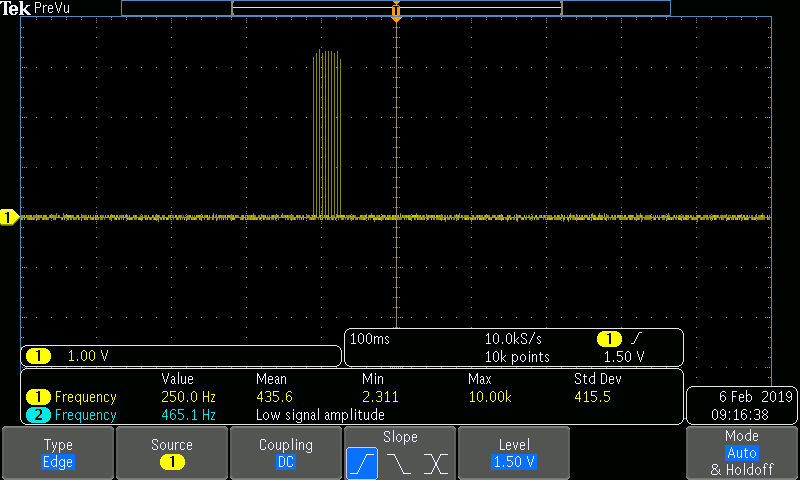

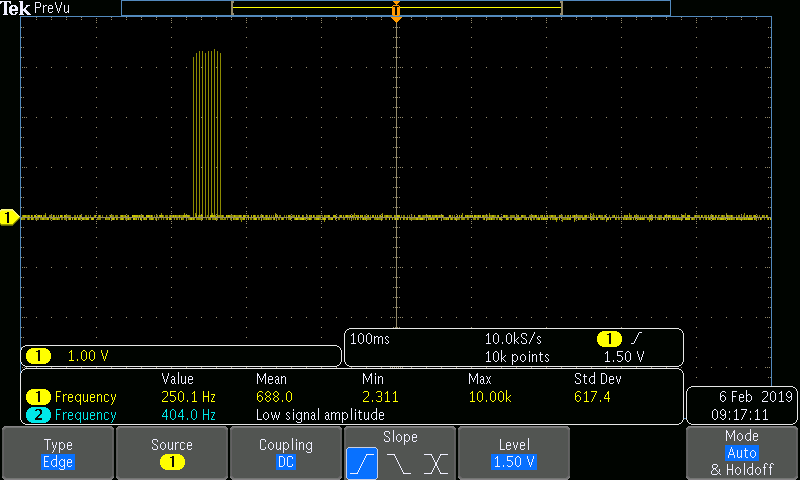

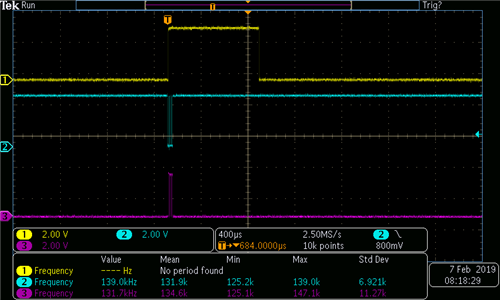

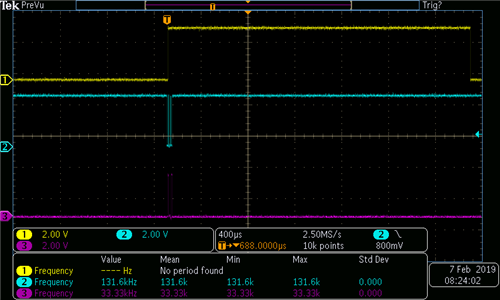

DRDY 线路假设为低电平有效、因此我预计电压在3.3V 时为高电平、但即使 ADC 处于待机模式、我也会在示波器上看到以下情况:

我担心 DRDY 线路需要使用上拉电阻器驱动、因此我在3.3V 连接了上拉电阻器、但问题仍然存在。 我已移除上拉电阻器、不确定还有什么可能出错。

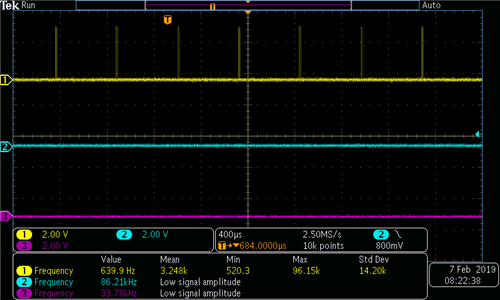

通信正常,所以我假设 DIN/DOUT/ SCLK/*CS 都正常。

*复位被拉高(3.3V)

* DONE 为开路状态,但在 ADC 内部上拉为高电平(3.3V)。

* DRDY 处于打开状态,用于探测。 我希望得到一个高信号、但得到上面显示的信号。

我们非常感谢您提供任何指导和帮助。