Other Parts Discussed in Thread: ADS1191, SN74LVC3G17, SN74LV1T34, ADS1298, ADS1294

主题中讨论的其他器件: SN74LVC3G17、 SN74LV1T34、 ADS1292、 ADS1298、 ADS1294

您好!

我还有一个问题...

下面、我首先要重点介绍 ADS1191。

我构建了以下电路:AVDD = 3.3V、DVDD = 1.8V

当我连接电路时、我希望 DRDY 在我将"启动"设置为"高电平"时立即开始脉冲、或者在我发送命令时立即更改其状态。

但是、线路始终保持低电平。

我可以通过某种方式测量芯片的全部功能、还是电路完全可用?

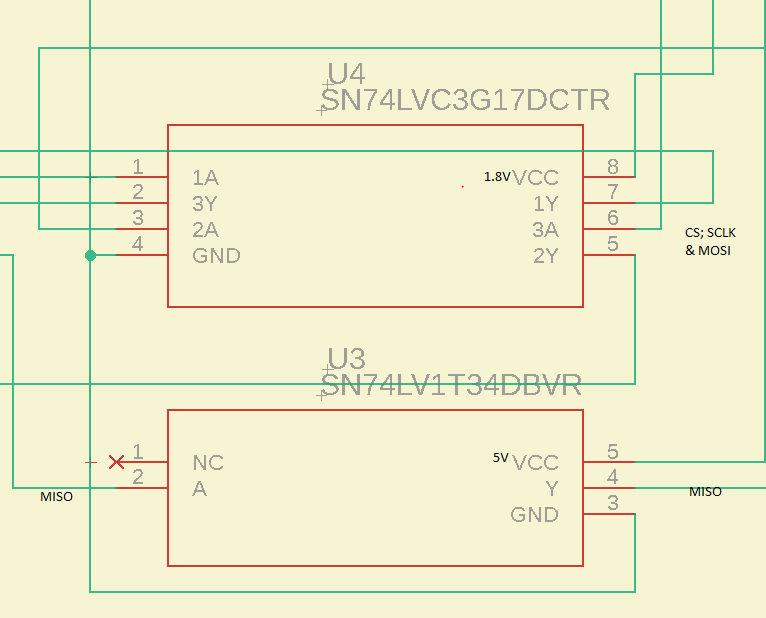

要转换我的5V 数字输入、我使用 SN74LVC3G17和 SN74LV1T34、如下所示:

提前非常感谢!

Hendrik