主题中讨论的其他器件:LMK61E2、 LMX2571

您好!

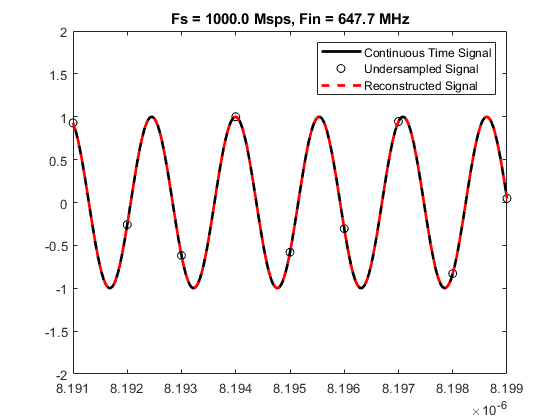

我正在使用 ADS 4225构建示波器、基于这样一个事实、即最大采样率不是1GS/s、而是125MS/s、我正在寻找一种充分利用其550MHz 带宽的方法。

一种方法是使用欠采样(针对重复信号)。 鉴于 ADC 的分辨率为12位、我需要一个抖动极低的时钟源。

为了进行欠采样、我必须精确测量输入信号的频率、然后生成精确的时钟频率、以便在正确的时间对输入信号进行采样。

示例:

输入信号:70MHz (第二奈奎斯特区域)

我需要一个1/70MHz + 1/100的70MHz 周期、即:14.285nS +(14.285/100)= 14.42785nS = 69.31MHz、以便在100个相邻周期中采集100个样本。

为了生成该频率、我需要具有一个低抖动时钟和一个 PLL、PLL 将编程生成我需要的采样频率、并最终以该频率驱动 ADC。

我已经选择了时钟 LMK61E2并考虑了 PLL LMX2571。

问题:

就采样频率而言、我的欠采样方法是否正确?

PLL 输出在抖动噪声方面会受到多大的影响?

还有其他建议吗?

提前感谢

Manos Tsachalidis