主题中讨论的其他器件:DAC39J84、 TSW14J10EVM

您好!

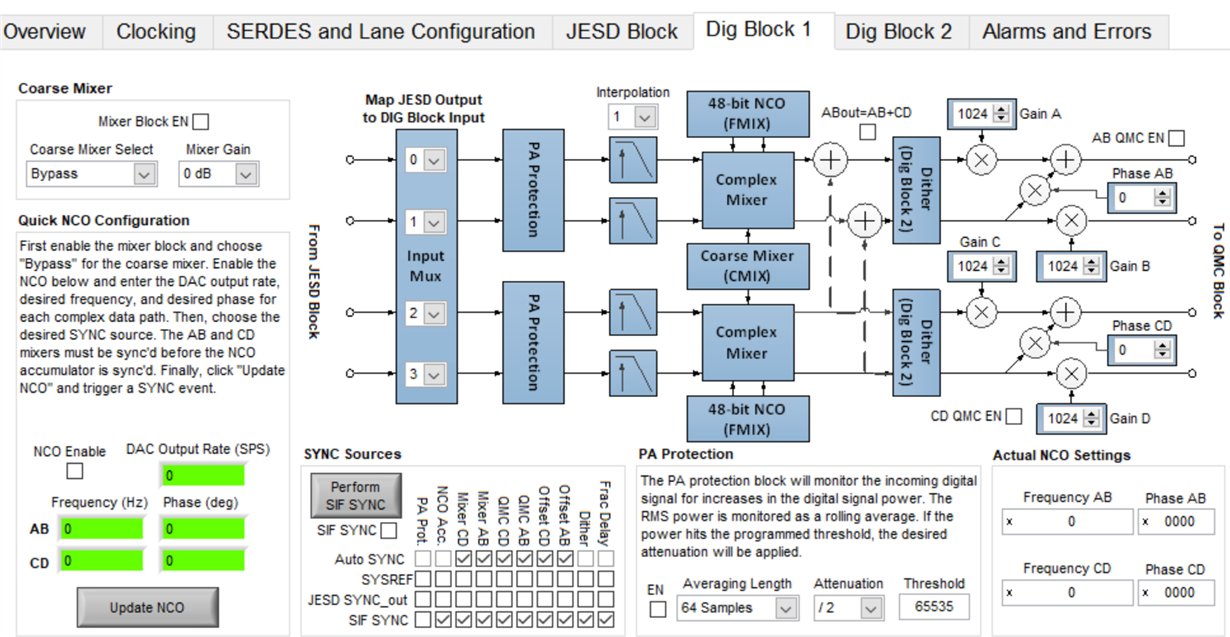

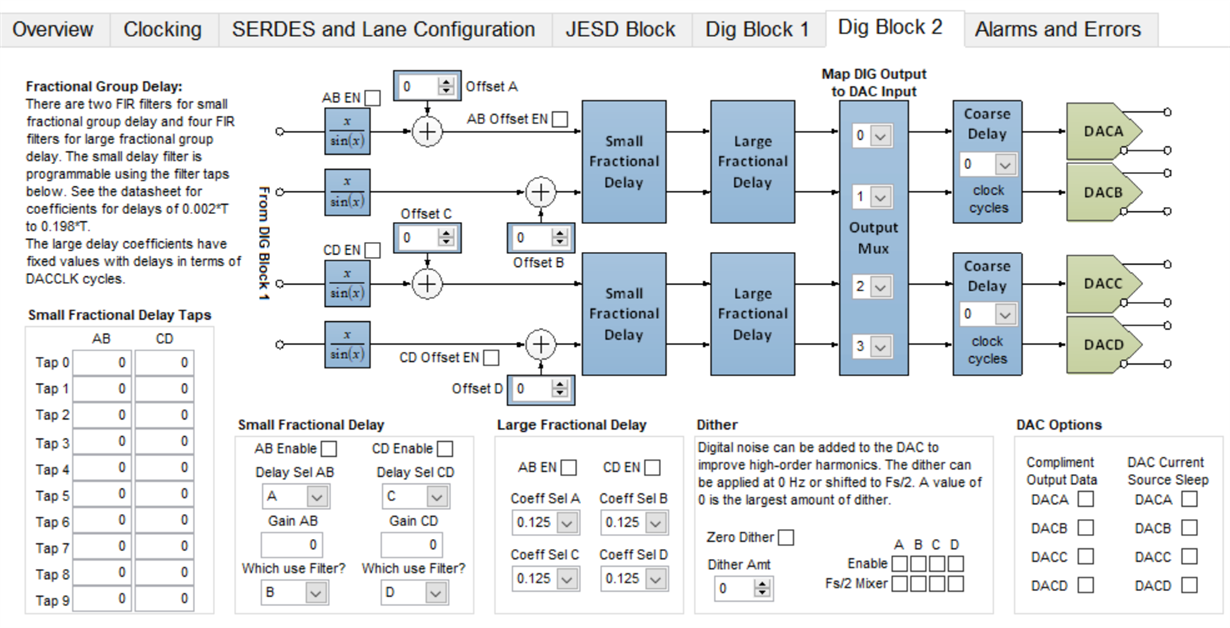

我 使用 Xilinx FPGA KC705来执行 DSP、并通过 DAC39J84将处理后的信号与 I、Q 信号一起传输。

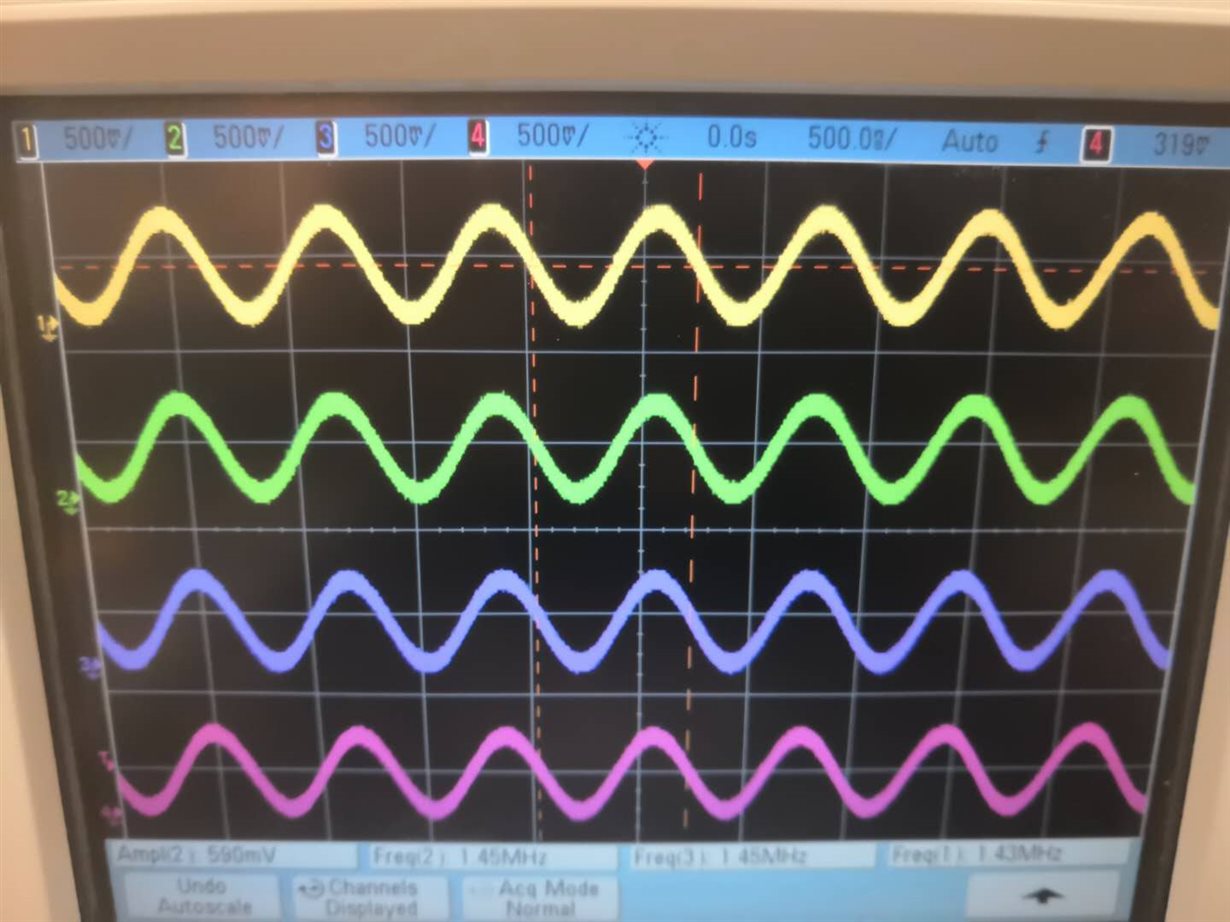

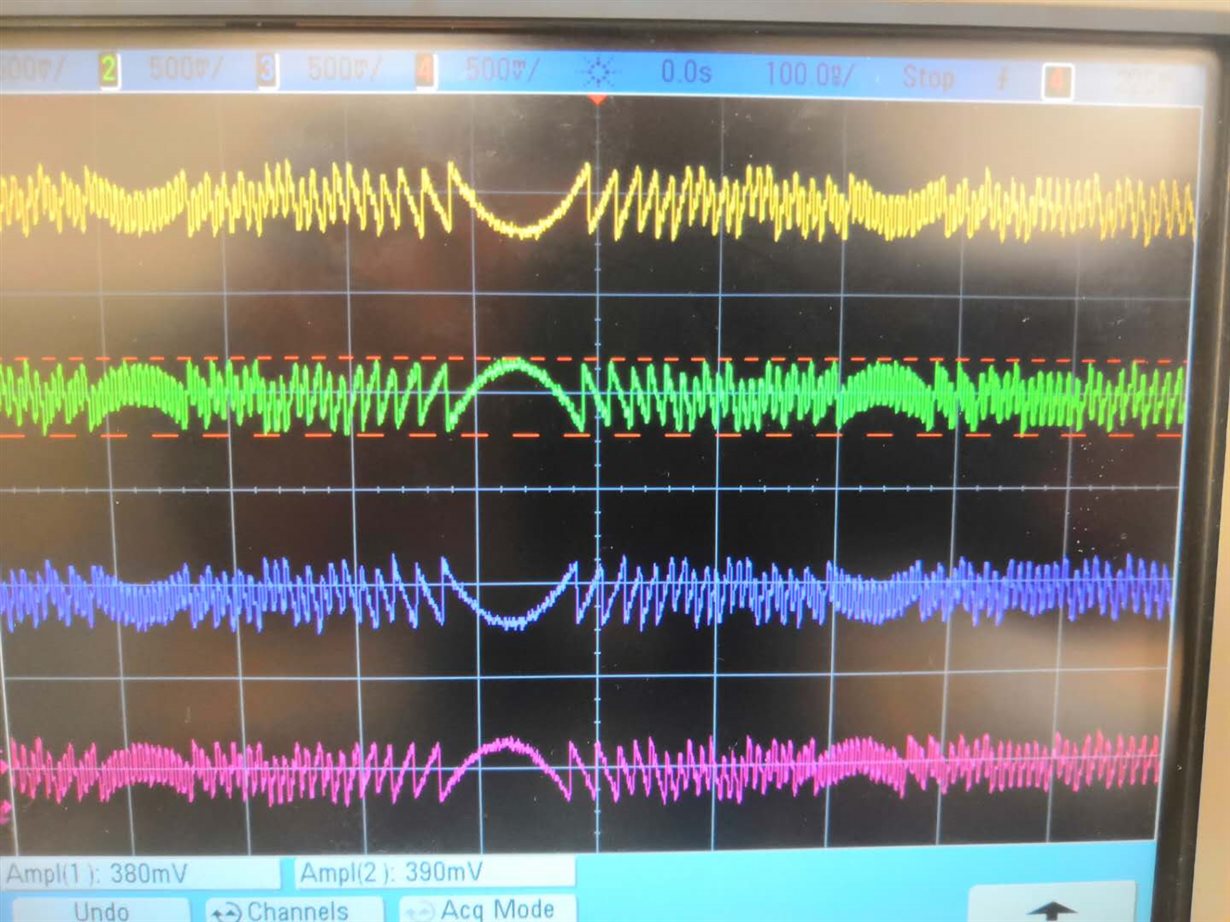

在第一阶段、我计划将 FPGA 与 JESD204标准中的 DAC 连接、以传输正弦波。

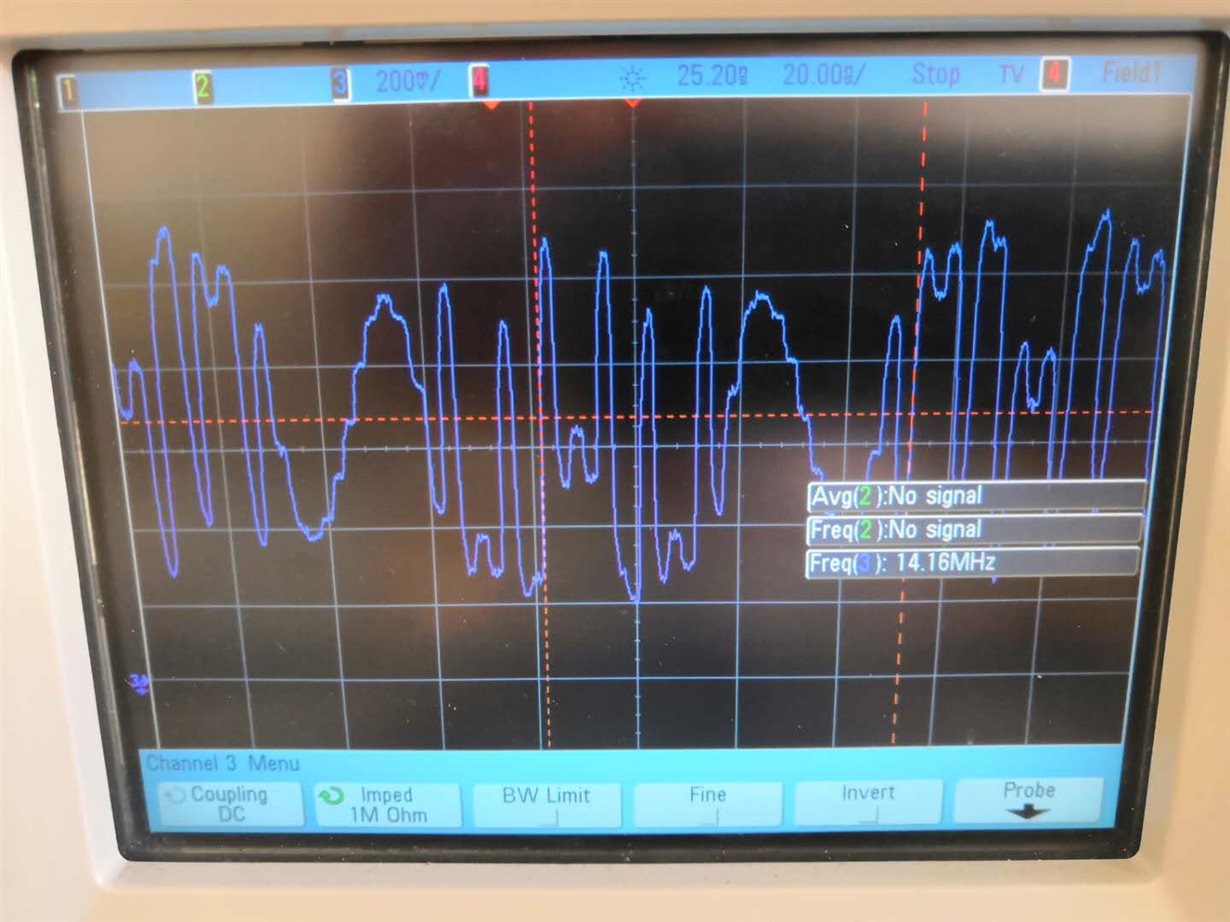

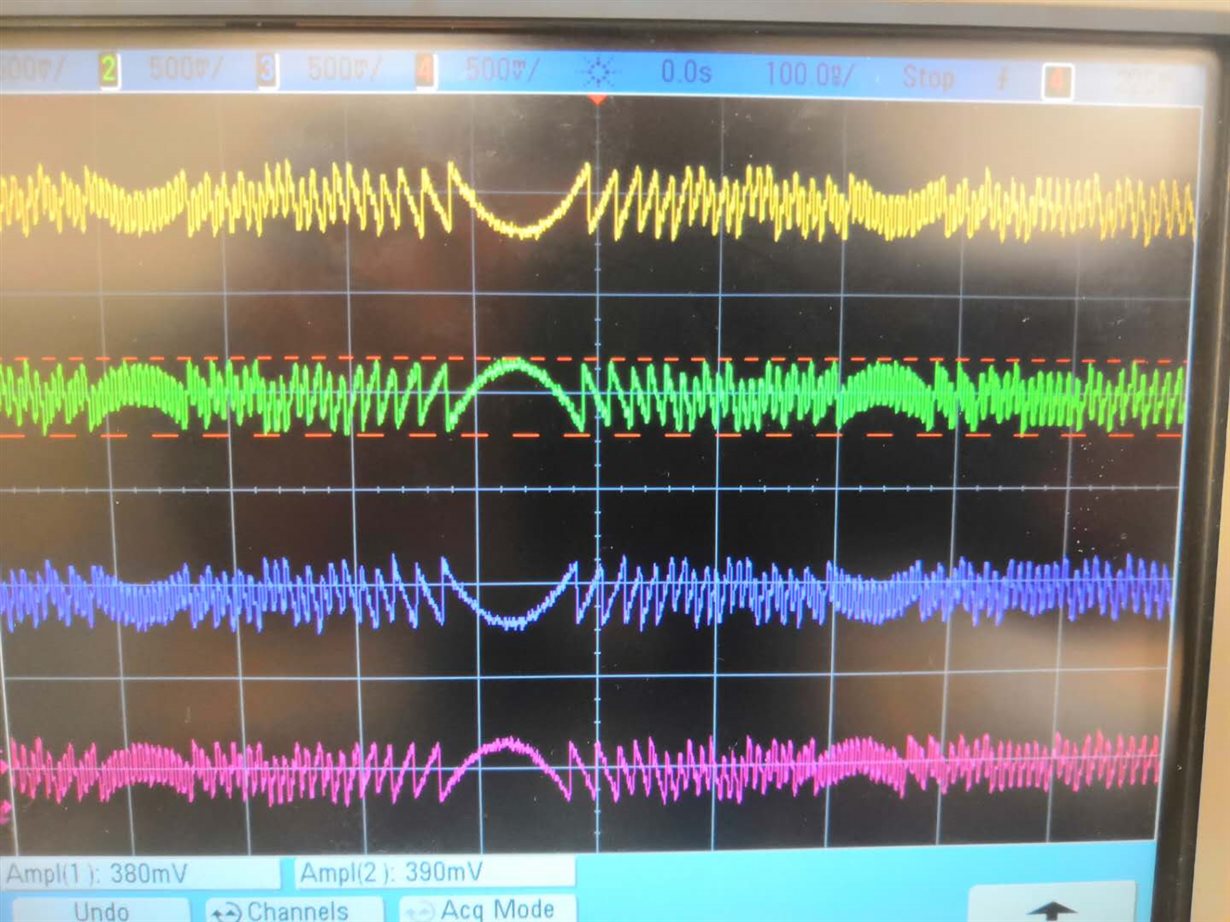

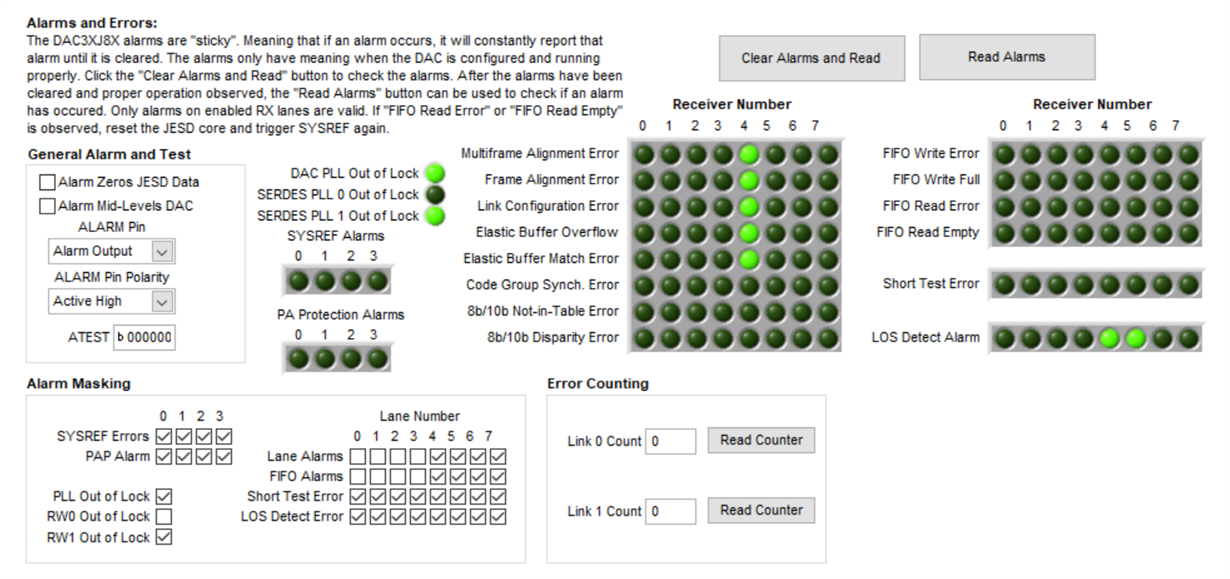

到目前为止、链路同步已实现。 但是、即使我匹配了所有配置参数、我也从 DAC 接收到失真信号。

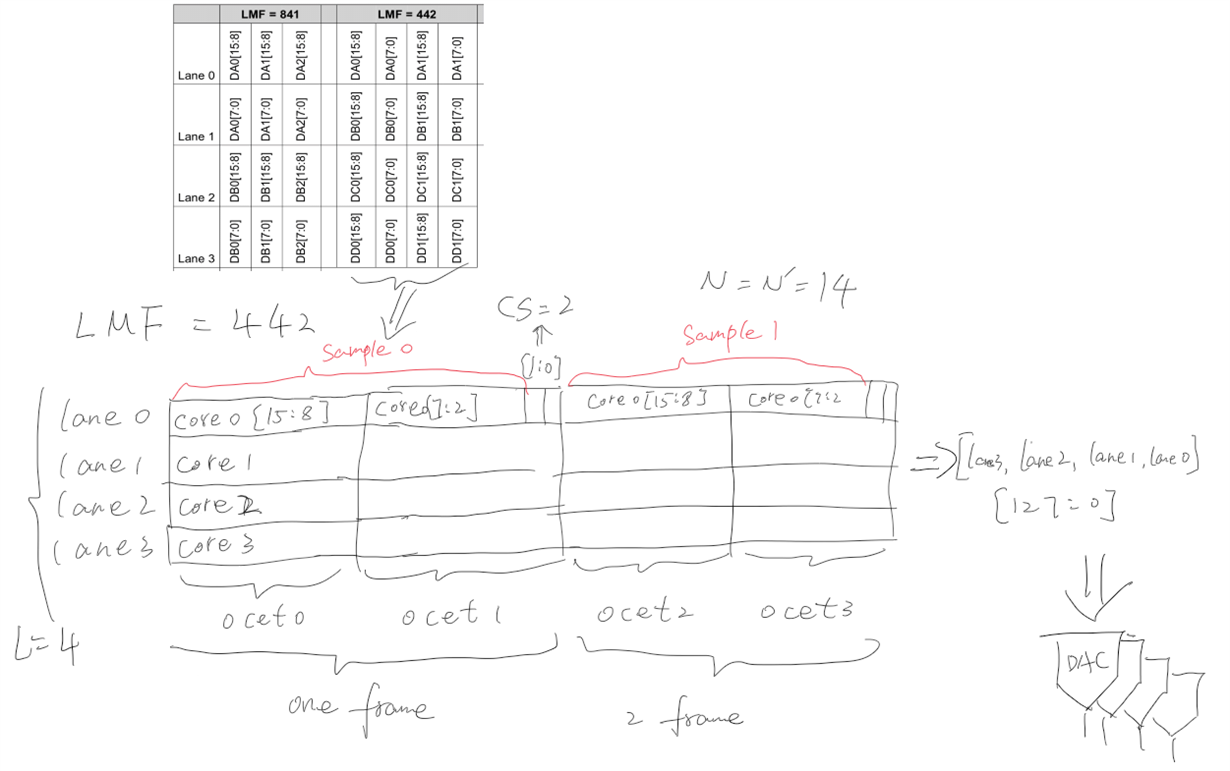

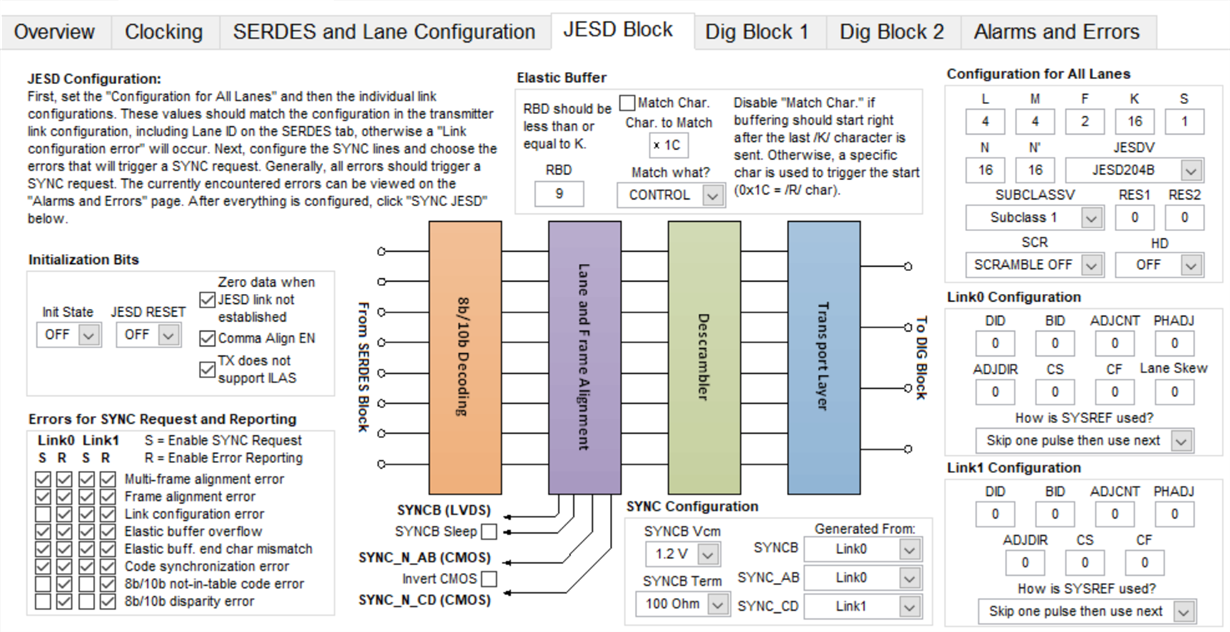

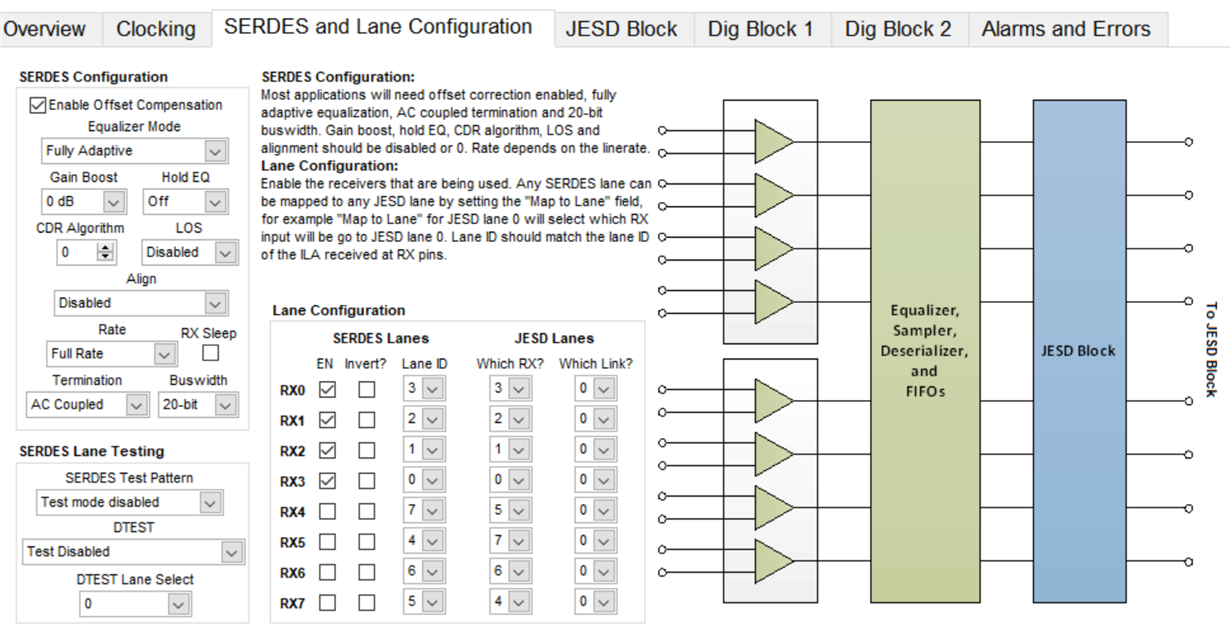

LMFS =4221 K=16 我在 DAC GUI 中设置这些参数

然后我将相应的寄存器值写入 FPGA 中的 JESD 内核

地址 x008

数据 x0000_0001启用通道对齐

地址 x00C

数据 x0000_0000 [0]禁用加扰

地址 x020

数据 x0000_0001 F (每帧八位位组)= 2

地址 x024

数据 x0000_000f K (每多帧数)= 16

ADDR x014,仅发送

数据 x0000_0003 [7:0] ILA 多帧= 4

仅限 ADDR x814 Tx

数据 x000_0100 [12:8] s=1

ADDR x810 ILA 配置4

数据 x0010_1004 [20:16] N'=16 [12:8] N=16 [7:0] M=4

是否有人可以就可能出现的问题向我提出一些建议?

感谢你的任何帮助。