Other Parts Discussed in Thread: DAC2900

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

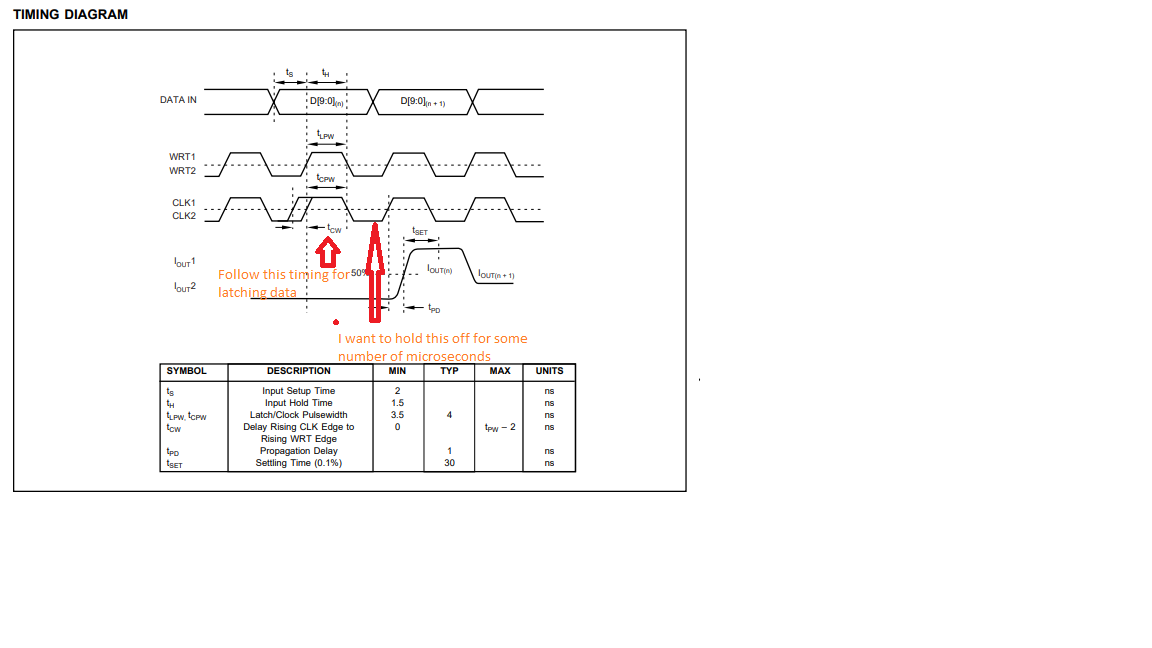

器件型号:DAC2900 大家好、我正在研究将 DAC2900用于我们这里的应用、我想以一种非常具体的方式使用它、我相信第5页上的时序图允许我的用例、但我希望得到确认:

我不想将写入和时钟信号绑定在一起。 我是从 FPGA 驱动的、因此我可以完全控制我的数据和控制输入信号。 我要做的是按照时序图中所示锁存数据、然后直到我指定未来的时间(可能是几微秒后)才执行第二个上升时钟边沿。 因此、我不会提供对称 时钟或写入信号、但我希望更多地将它们用作真正的锁存信号。

时钟或写入信号、但我希望更多地将它们用作真正的锁存信号。

时序图没有指出低脉冲宽度、因此我认为如果我遵循 tlpw、tcpw、TCW、那么我将能够执行我想要的操作。 这是真的吗? 我能否提供非对称时钟信号?