主题中讨论的其他器件:ADS54J42、 ADS54J40、 TSW14J57EVM

尊敬的 TI 专家:

我一直在尝试将 ADS54J42 EVM 与 Intel Arria 10 FPGA 开发板连接。 我已通过 FMC 连接它们。 到目前为止、我没有成功。

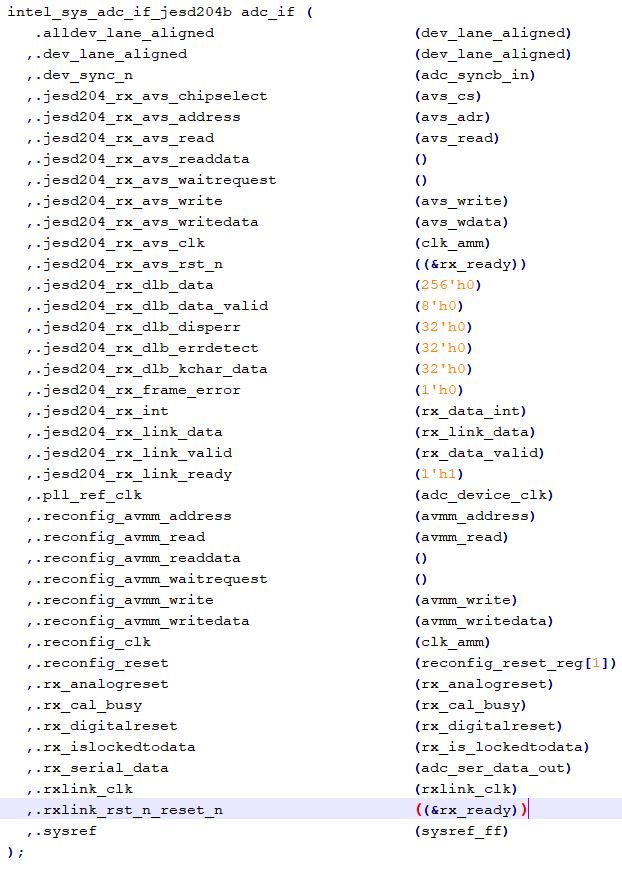

更确切地说, 我的 FPGA 上的 JESD204B 模块配置为接收器,具有子类1、2500Mbps 数据速率、启用软 PC、62.5MHz 参考时钟、LMFS = 8224、K = 32、N = 14、N’= 16, 并启用扰频(尽管我认为这不应影响链路序列)。

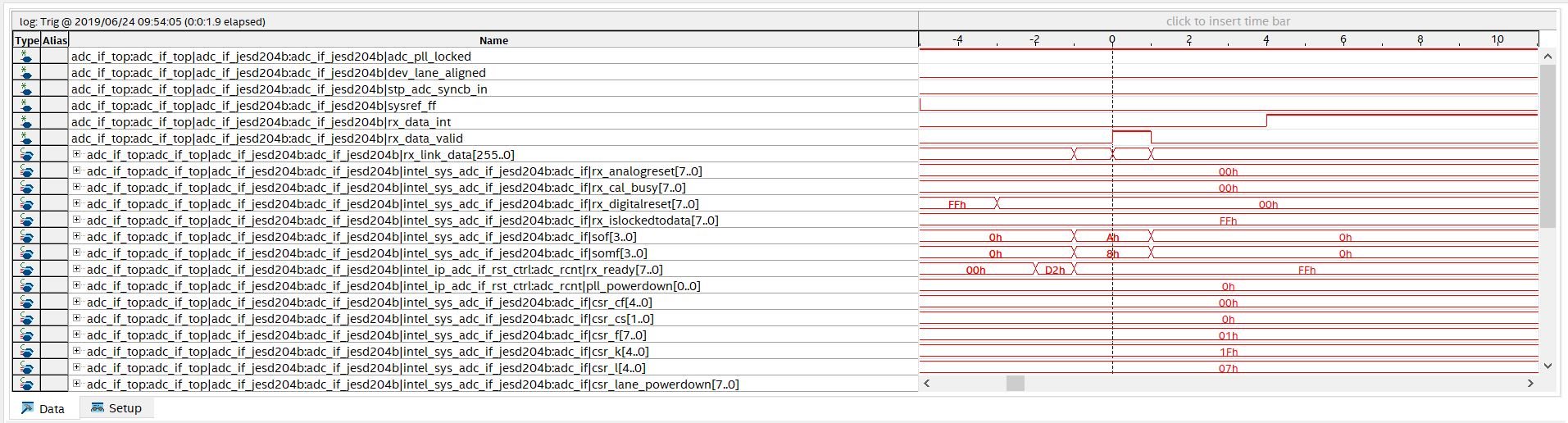

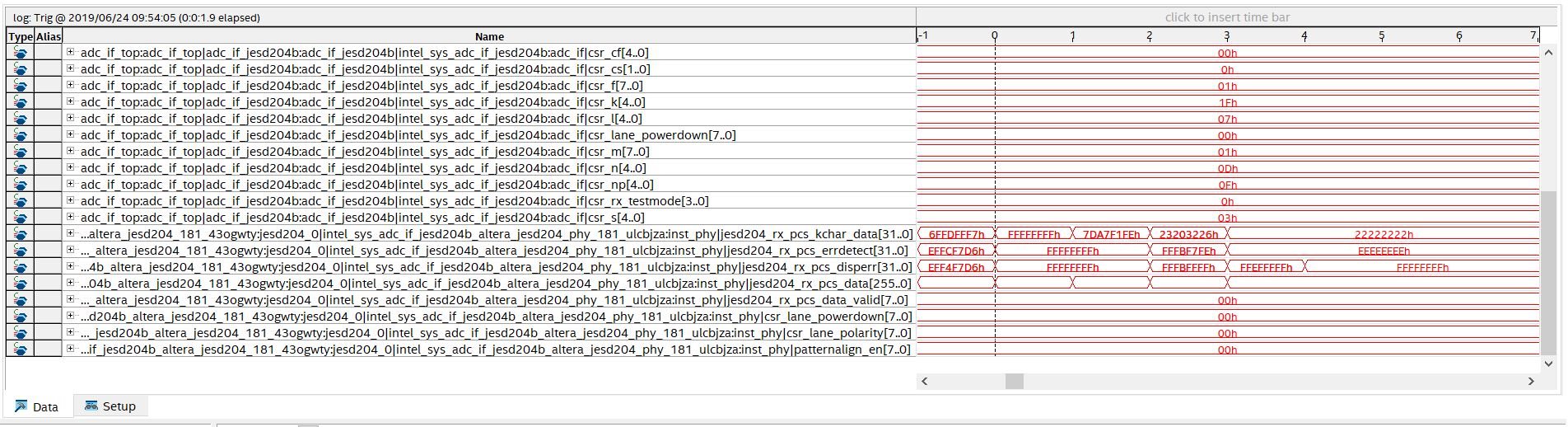

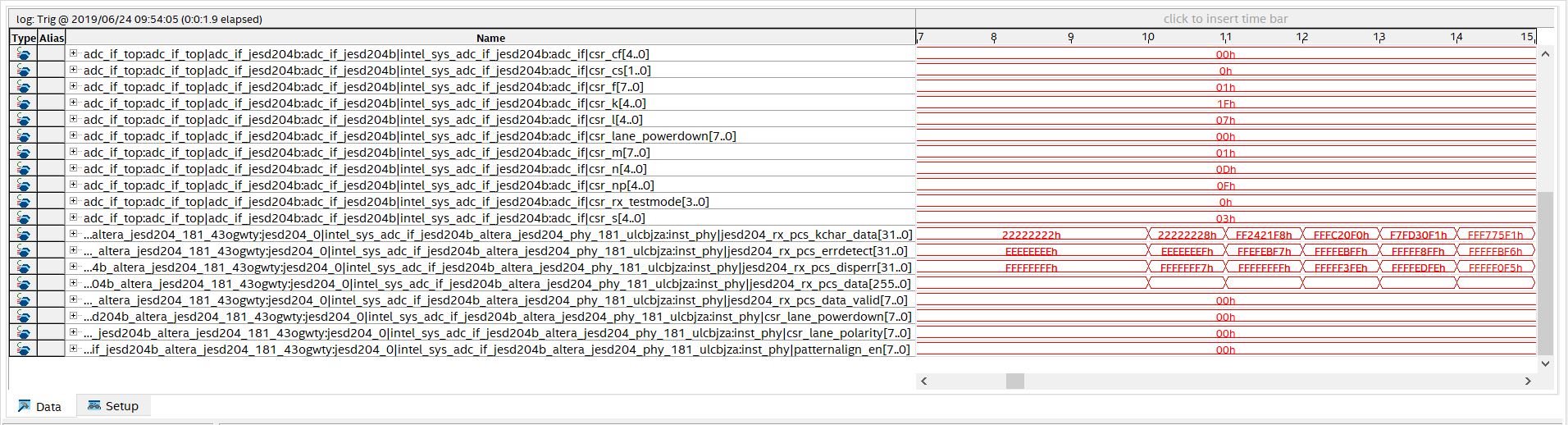

我正在使用英特尔的信号分路器来捕获进入/来自接口的信号。 下面是一些屏幕截图:

RX_islockedtodata 从 JESD IF 输入到我的复位控制器。 它从某些值(屏幕截图中为0xEF)变为0xFF。 一段时间后、Rx_digitalreset (如果来自复位控制器、则为 JESD 输入)从0xFF 变为0x00、Rx_READY (如果来自复位控制器、则为 JESD 输入)从某个值(屏幕截图中为0xD2)变为0xFF。 我认为这是为了表明所有通道都已就绪。

此时、Rx_DATA_VALID 脉冲、然后中断信号 Rx_DATA_INT 会持续一段时间。 一旦它被取消置位、数字复位信号再次为0xFF、并且 Rx_islockedtodata 返回到某些非0xFF 值(屏幕截图中的0xFB)。

在我的仿真中、我希望在这个复位序列之后:

- RX_Is_lockedtodata 0x00 -> 0xFF

- RX_digitalreset 0xFF -> 0x00 & RX_READY 0x00 -> 0xFF

ADC_syncb_in 信号将被置为有效、后跟 DEV_lane 对齐。 之后、Rx_DATA_VALID 将使用来自串行数据引脚的有效数据进行置位。 中断信号未生效。

我已随附了针对 ADC EVM 板的此链路测试提供给我的 cfg 文件。 对于 LMK 的500MHz 外部时钟输入、说明如下:

1.启动 ADC54Jxx EVM GUI

2.确认 GUI 上的 USB 状态 LED 亮起

3.在“低级视图”选项卡中加载 LMK_Config_External_Clock.cfg

4.确认 D1和 D2 LED 不亮

5.按 SW1进行 ADC 复位

6.在“低级视图”选项卡中加载 ADS54J40_LMF_8224_K32.cfg

我被骗了、希望您能有深入的了解。 以下是我的一些问题:

1.在给定附加的配置文件的情况下、ADC 配置是否正确?

2.在给定附加的配置文件的情况下、LMK 时钟源配置是否正确? 器件时钟的预期时钟输出为62.5MHz、系统参考时钟的预期时钟输出为3.90625MHz、用于 J6 LMK_CLKIN 端口的外部500MHz 参考时钟输入。

3.由于我使用的是外部时钟源、我是否必须去除水份 SJP2中的分流器组件?

4.我是否应该使用 CLK_LAO_0信号? 目前、我在62.5MHz 器件时钟上使用 FPGA_JESD_CLK。 该信号作为 PLL_ref_clk 信号输入到 JESD 接口模块。 我的 rxlink_clk 也是62.5MHz 时钟、它是另一个 PLL 的输出、该 PLL 使用 FPGA_JESD_CLK 作为输出62.5MHz rxlink_clk (以及系统的一些其他时钟)的参考。

很抱歉这篇长文章、并提前感谢您的任何见解。

此致、

Abdul

e2e.ti.com/.../ADS54J40_5F00_LMF_5F00_8224_5F00_K32.cfge2e.ti.com/.../LMK_5F00_Config_5F00_External_5F00_Clock.cfg