主题中讨论的其他器件: ADC16DX370

尊敬的支持者:

我正在使用 Arria 10 SoC 开发套件与 Abaco FMC144的定制集成。

时钟生成和模数转换正在执行正常、但还不幸运的是、通过 JESD 链路连接到 DAC38J84。

SYSREF 是一个2脉冲序列、频率为 DACCLK 的1/32、即148.5MHz。

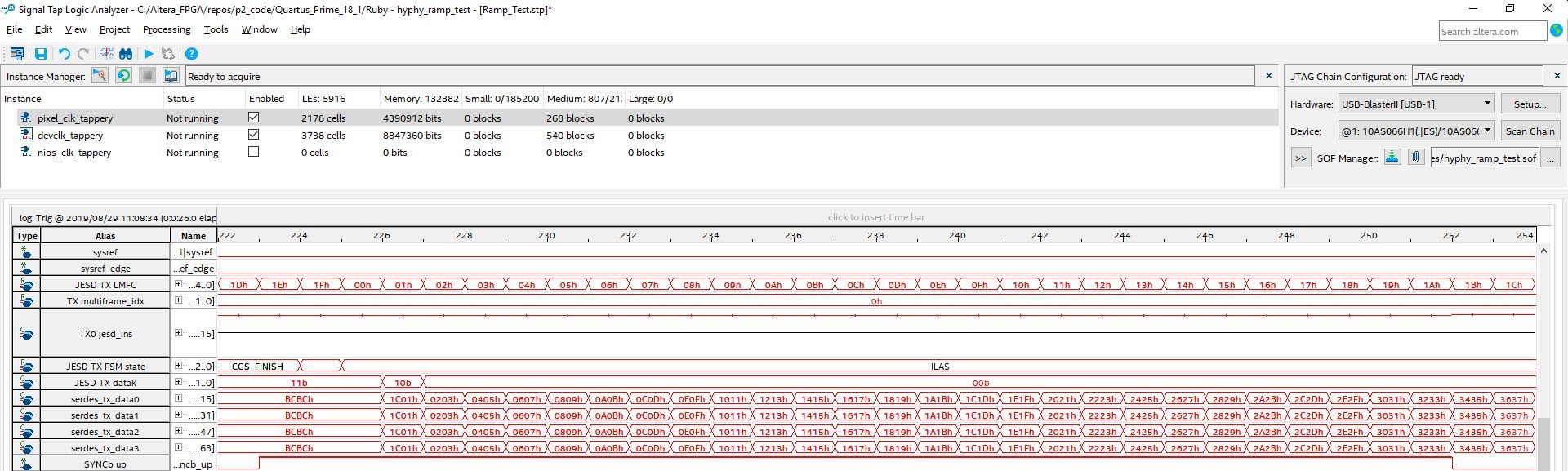

K = 32在我们的设置中、LMF 为442。

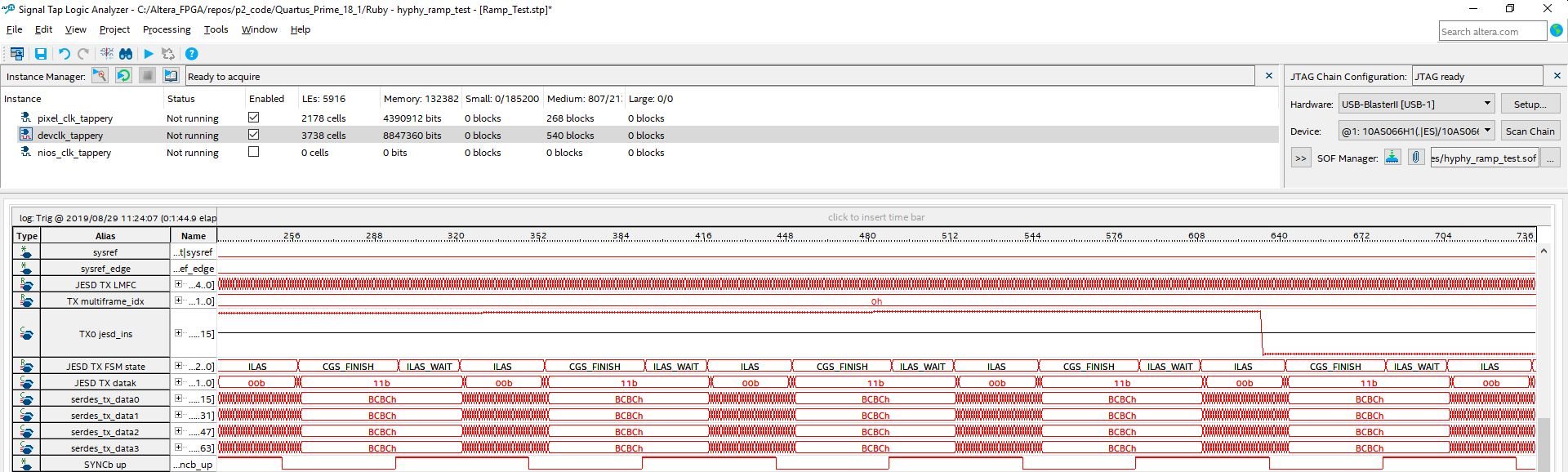

SignalTap 显示与 DAC 芯片的 JESD 链路已短暂建立、但该行为会无限期重复:DAC 芯片将 SYNCb 置为有效、然后在接收到一系列 K28.5符号后将 SYNCb 置为无效、但随后在 ILA 序列期间的不同点(通常在第3个多帧中)将 SYNCb 置为有效。 SYSREF 脉冲之后的通道警报快照仅在1或2个通道中显示帧对齐错误、而其他错误标志则为清除。

基于之前的线程、我已经尝试清除0x51[7:0]、这应该会抑制触发 SYNCb 时产生的任何错误。 但是、在此设置中、SignalTap 显示 SYNCb 在短时间内非法置为有效。

您能否提供一些有关导致此 SYNCb 行为的原因的见解?

满怀希望地感谢--Todd