大家好、

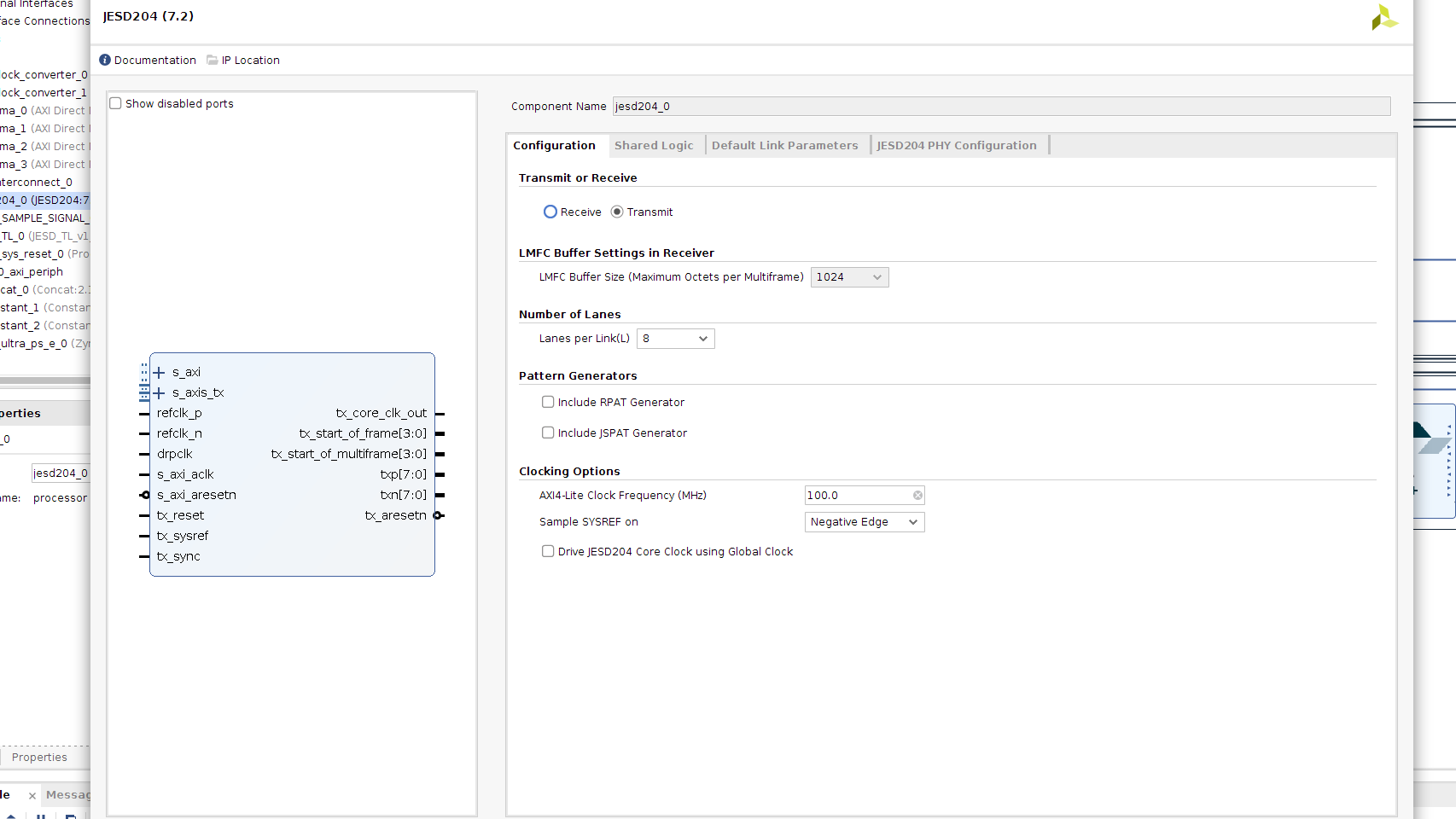

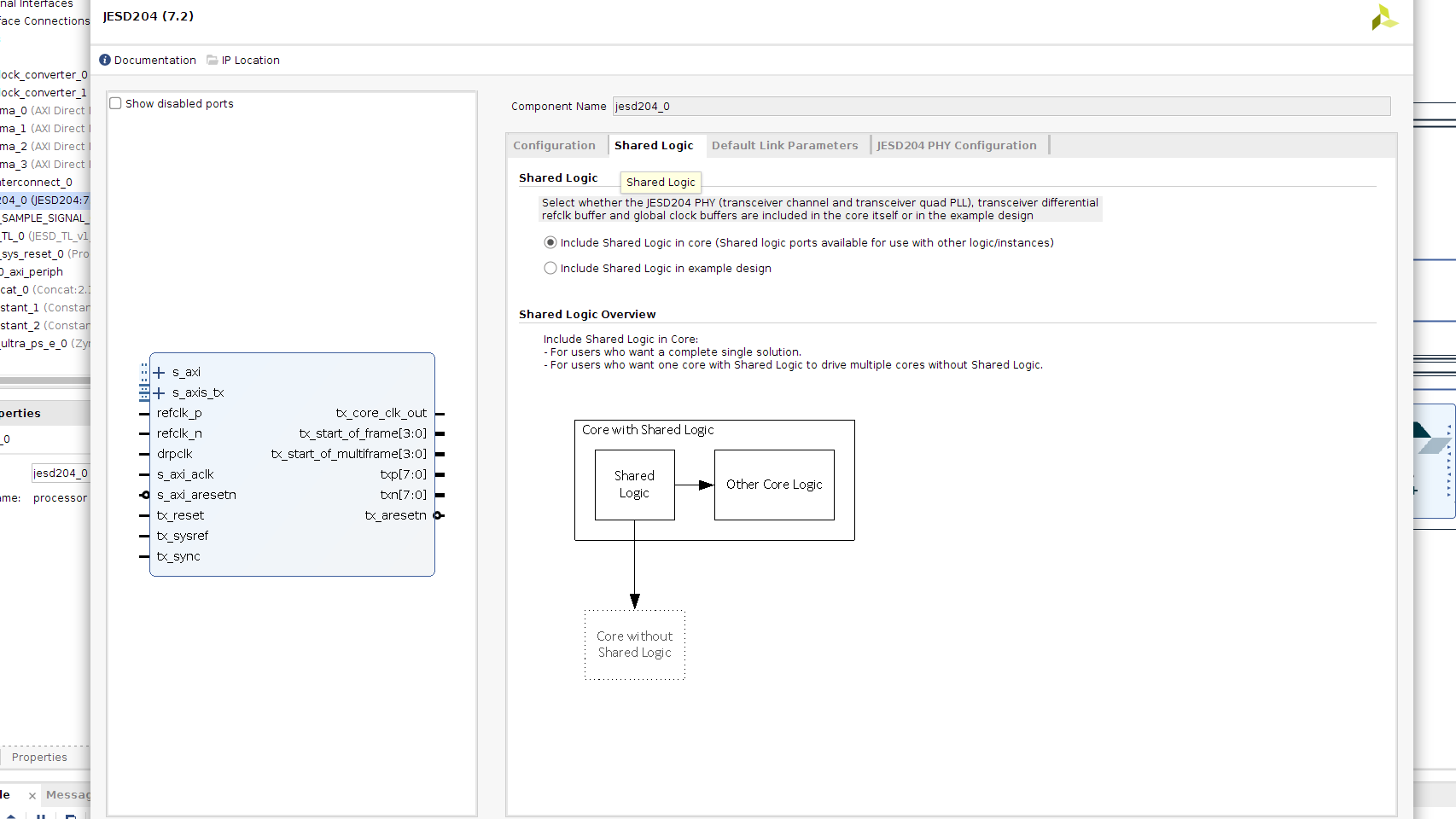

我尝试 从 UltraScale+ JESD 块向 DAC39J84发送数据。

我的设计可与评估板配合使用(http://www.ti.com/tool/DAC37J84EVM)

但是、在定制构建板上、来自 DAC 的 SYNC 信号的性能未达到预期。

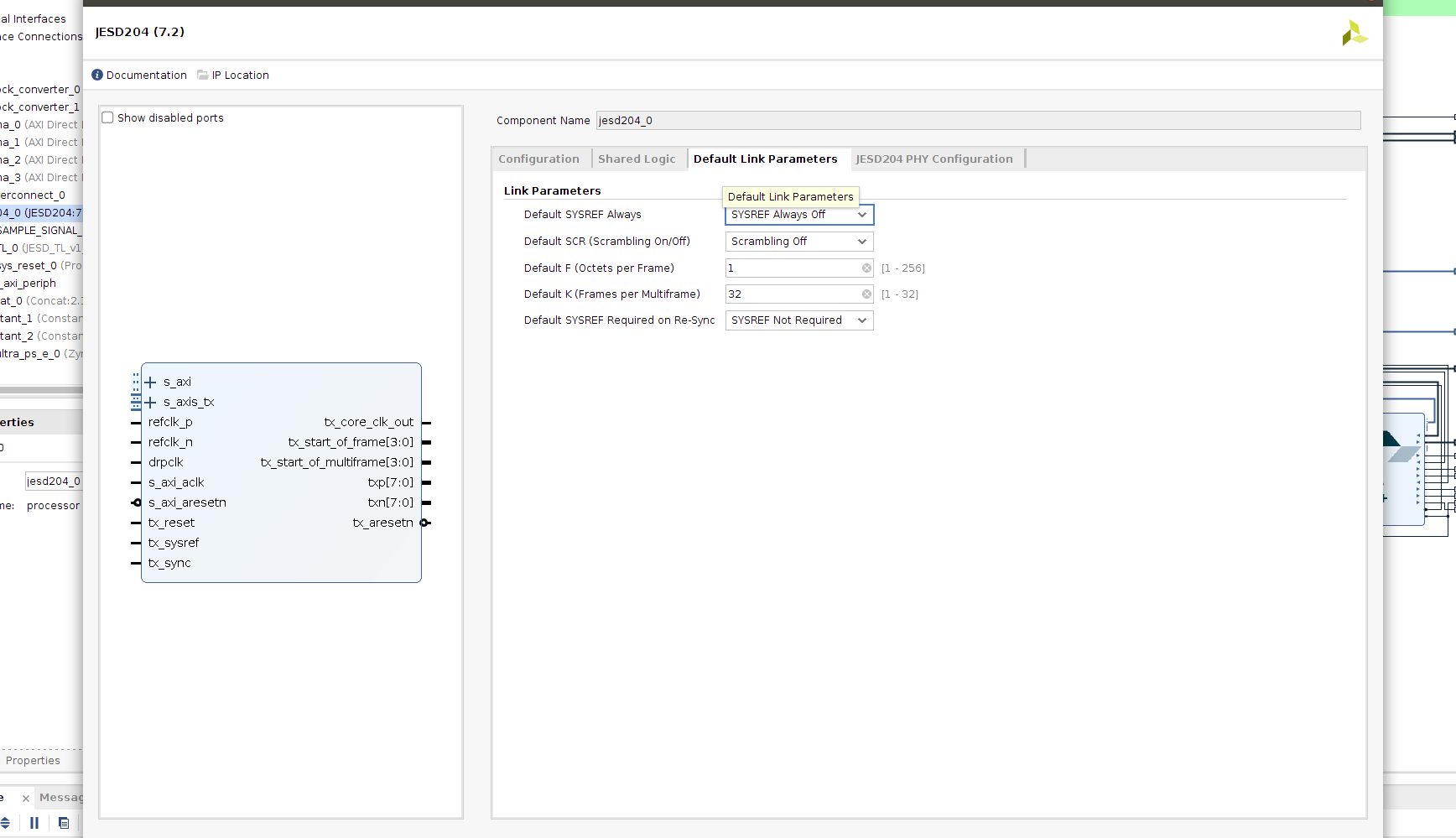

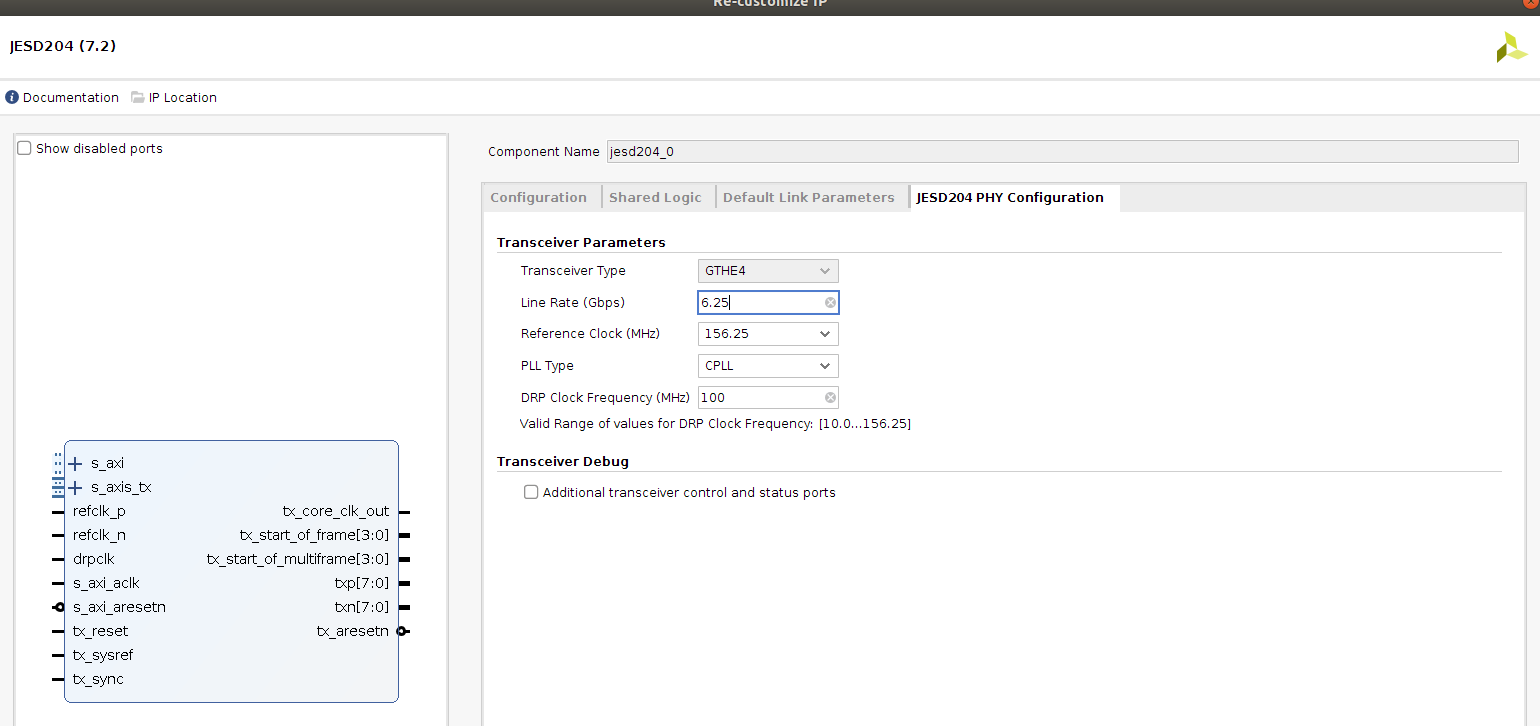

我的 JESD 设计:子类1、8通道、F = 1、K = 20、线路速率= 6.25Gbps、参考时钟= 156.25、Sysref = 4.88 (DAC 和 FPGA 的 sysref 相同)、DAC clk = 625MHz。

同样、该设计在评估板上工作正常、定制板的布局 非常相似。 我检查了 DAC 和时钟 分配器(LTC6981)的时钟和 SPI 配置、它们按预期运行、电压电平正常。

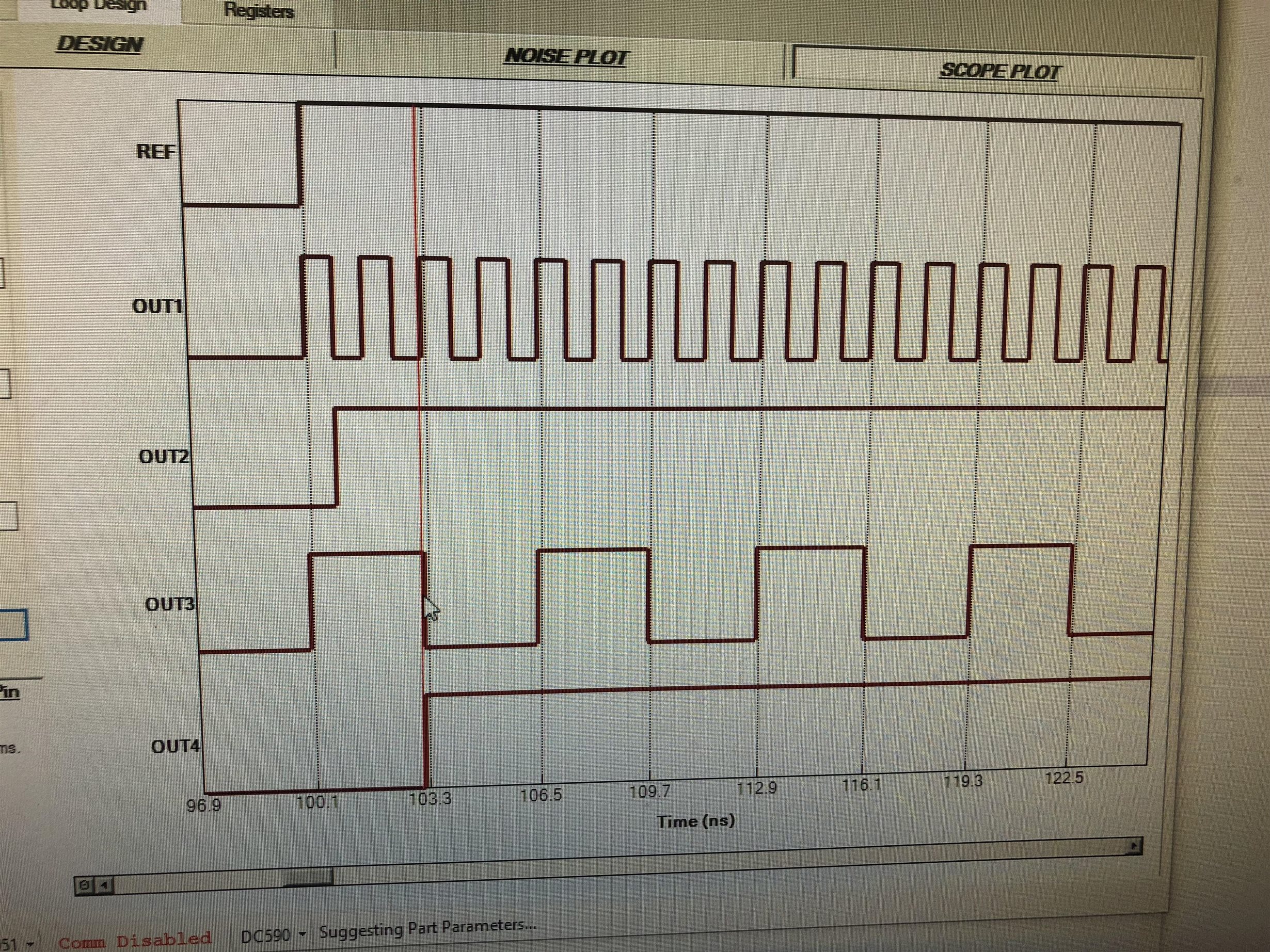

时钟:

OUT1 -> DAC 时钟= 625MHz

OUT2 -> DAC SYSREF = 4.88Mhz

OUT3 -> FPGA REFCLK = 156.25Mhz

OUT4 -> FPGA SYSREF = 4.88Mhz

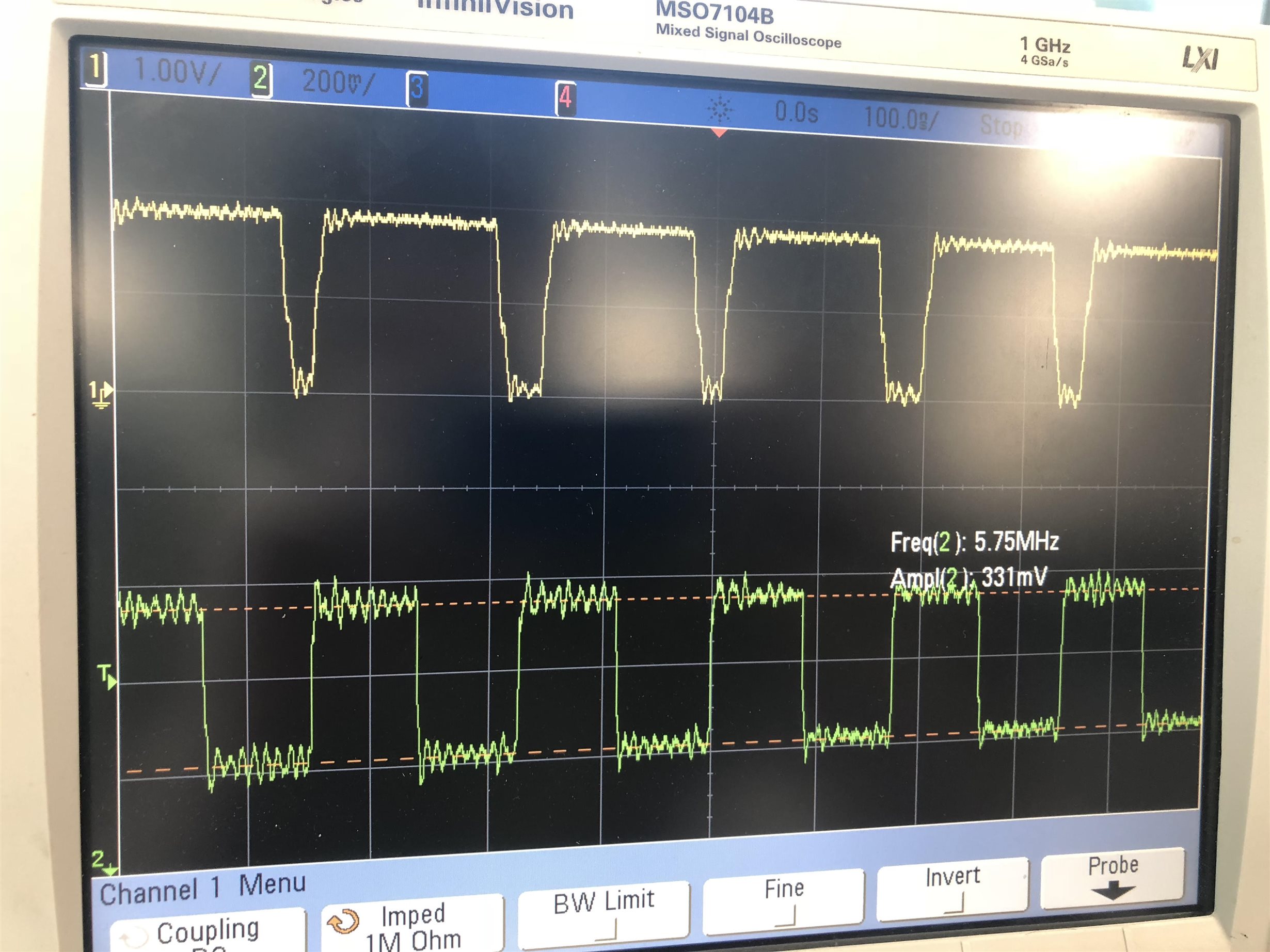

这是评估板上发生的情况(顶部->同步;底部-> sysref):

在定制电路板上、SYNC 始终为高电平、我不确定是什么原因导致的。 显然,这是一个普遍的问题:

https://e2e.ti.com/support/data-converters/f/73/p/574027/2131081?tisearch=e2e-sitesearch&keymatch=DAC39J84#pi320995=4

https://forums.xilinx.com/t5/Networking-and-Connectivity/JESD-RX-sync-not-asserted/td-p/892775

流程如下:

1)对时钟 分配器进行编程并对齐输出(它提供 DAC 时钟和 FPGA 时钟;两个 SYSREF 时钟均为静音)

2)对 FPGA 进行编程

3)对 DAC 进行编程(此处 SYNC 变为高电平、永远不会改变)

4)电源 SYSREF ~ 1秒(此处 SYNC 引脚应开始切换)

5)注意:JESD IP 内核在连接 TX_迎宾 饰引脚时可以看到参考频率

此外、同步需要切换什么? 它是在寻找 SYSREF 边沿还是 K28.5符号?

有什么想法吗?