我正在尝试使用 ADS8363及其公布的1MHz 采样率,并且忙信号的行为有一些问题。 我使用的是全时钟模式1,其中40MHz 时钟和通道信息被禁用(CID=1)。 我将 RD 和 CONVST 连接在一起,因此无法单独控制它们。

数据表规定(表7.9开关特性、t_D2)、在全时钟模式下、BUSY 信号应该在第24个上升边沿之后转换为低电平。 但是、图2中的时序图似乎显示了第25个上升沿。 实际上,我在设置中看到了这两个变体,我可以通过插入额外的时钟周期在它们之间进行切换。 通常、我每次转换输出40个时钟周期、但一次转换使用41个周期会在第24或25个上升沿的 BUSY 变为低电平之间切换。

因此、通常我会假设情况最差、然后在第25个周期开始读取、但数据的 LSB 会与下一次转换重叠。 当将 CONVST/RD 设置为高电平时、ADC 似乎将 SDOx 驱动为低电平、并且我的 LSB 始终为0。 类似地、在第24个周期开始读取会在 BUSY 在第25个上升沿变为低电平时提供一个损坏的 MSB。

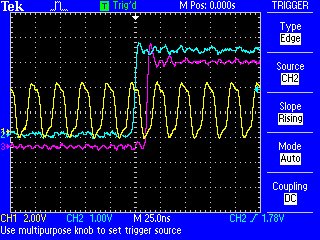

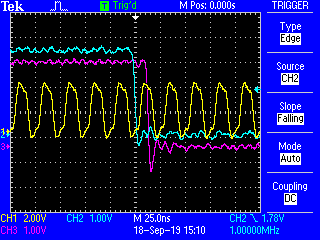

如何在采样率为1MHz 的全时钟模式下使用 ADS8363? 我已附上一些显示 CONVST/RD 时间的屏幕截图。 信号如下:CH1 -> CLK、CH2 -> CONVST/RD、CH3 -> BUSY。

CONVST 上升沿:

CONVST 下降沿: