尊敬的 TI:

我发布这篇文章是为了了解如何将 ADC12DJ3200的时间戳输入与 Virtex-7 FPGA 连接。

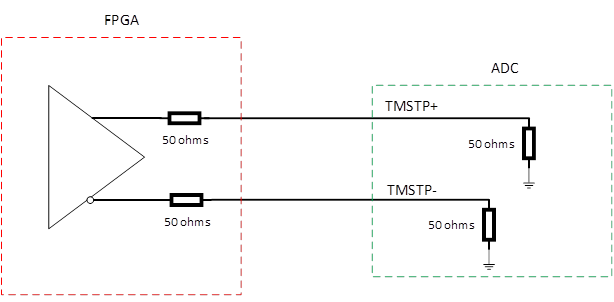

在这篇文章中 、Jim Brinkhurst1 建议 在 v7 FPGA 和 ADC12DJ3200时间戳输入之间使用 MC100LVEP11缓冲器、并提供了一个方框图、显示了该缓冲器的输出与 ADC12DJ3200的时间戳输入之间的连接。 该图如下所示:

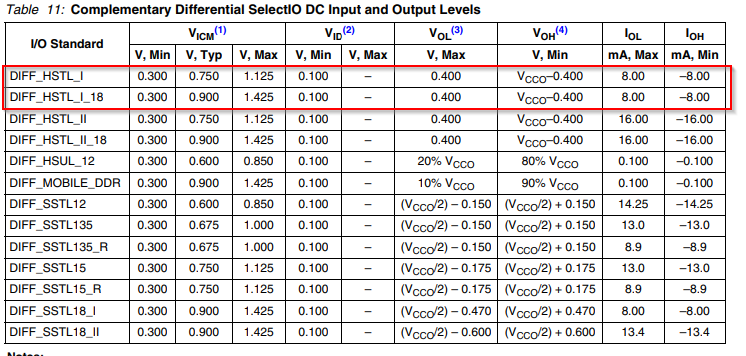

对于此连接,Jim 建议使用50欧姆(上图中标记为红色),此缓冲器的共模输出将为0.58v,如果我们将50欧姆更改为75欧姆, 然后 、MC100LVEP11缓冲器的共模输出将在 ADC12DJ3200时间戳输入共模要求(<0.55v)范围内。

ADC12DJ3200的数据表中提到、时间戳输入需要使用建议的交流耦合或直流耦合共模电压进行外部偏置。

现在 ,在 MC100LVEP11的数据表中,给出了一个图,显示了如何进行端接。 它们使用50欧姆电阻器将 P 和 N 信号端接到 VTT (VTT= VCC-2V)、如下所示:

但 Jim Brinkhurst1 提供的图显示、缓冲器输出端只有50欧姆电阻器、另有50欧姆串联电阻器位于 ADC12DJ3200时间戳输入内部、而这50欧姆电阻器未连接到 ADC12DJ3200外部或内部的任何 VTT。

那么、如何为 ADC12DJ3200时间戳输入提供共模电压?

另外、如果 我们按照下图进行连接、你们还能告诉我使用哪个公式来计算 MC100LVEP11缓冲器的0.58v 共模输出电压:

我们将非常感谢尽早作出反应。

谢谢、

Lalit