您好!

我对 ADS5562有疑问。

-采样频率:12.5MHz

-低速模式(将 SCLK 引脚连接至高电平)

-CMOS 模式

[第1季度]

它们的 CLKOUT (5引脚)占空比不是50%。

其测量结果约为78%。

这是为什么?

是否存在导致上述问题的任何可能原因?

- LVDS 和 CMOS 模式的 D/S、P15、6.11时序特性

并行 CMOS 模式:CMOS 输出时钟占空比= 50%

以下数据的测量条件为默认速度模式。

我认为它在低速模式下使用时可能不适用。

CLKout 的重要作用不是占空比、而是上升沿。

因此、我认为我不需要担心占空比不是50%。

[第2季度]

我要求他们调查波形、看看它们是否满足以下条件:

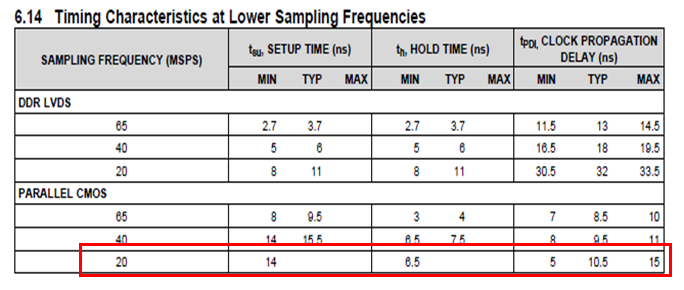

-较低采样频率下的 D/S、p16、6.14时序特性

- D/S、P18、 图5。 CMOS 模式时序

因此、

tPDI =约70ns。

Tsu =约25ns

TH =大约55ns

这一结果似乎不符合要求。

这是为什么?

是否存在导致上述问题的任何可能原因?

此外、我认为即使使用 SEN 控制引脚调整输出时钟位置、也无法满足请求。

我应该怎么做?

此致、

Kaede Kudo