我正在处理一个客户问题、即 FPGA 无法通过 SPI 端口与 ADS1258通信。 他们 已经尝试过 TI 网站上的示例 C 程序。 我们能够控制 PWDN 和复位引脚。 START 和 CLKSEL 通过硬接线保持高电平。 CS、SDI、SCLK 和 SDO 连接到 FPGA SPI 引脚。 FPGA 固件具有德州仪器模式、可保持时钟持续运行。 这似乎是必要的、因为数据表显示"如果 SCLK 在4096或256个 fclk 周期内保持未激活状态、正在进行的读取或写入操作将终止并且 SPI 接口复位。"

还有其他 FPGA 模式不是这样做的。 我们已成功地将不同模式用于不同的 TI 模数转换器。

问题:

1.我们是否需要使 SCLK 线路在此器件上以这种方式运行?

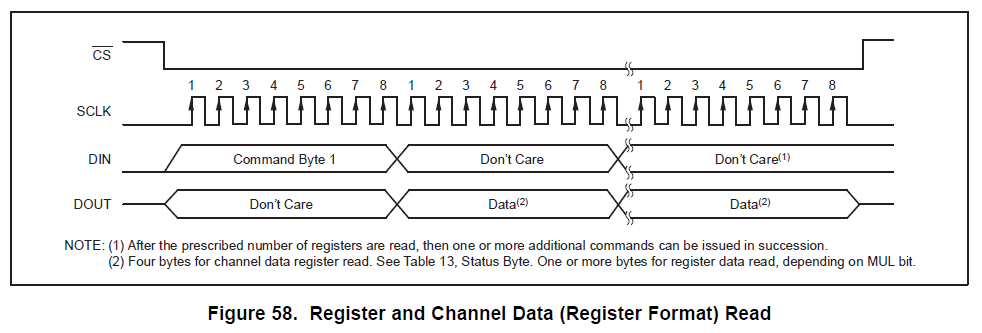

2.示例代码似乎通过 SPI 以8位块的形式读取数据和状态信号。 这是我们需要做的吗?

3、成功运行时、是否有任何 SPI 信号的示例?

我已附上示波器屏幕截图、其中显示了尝试进行通信的情况。 您可以看到时钟持续运行。 CS 在通信开始时变为高电平。 SDI 引脚通过尝试命令切换。 不过、SDO 引脚似乎几乎是随机通信。