请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DAC39J84 你(们)好

如果您能回答有关 DAC39J84的这两个问题、我将不胜感激。

1 -在 DAC39J84数据表图75中、已显示对于使用 LVPECL 发送信号的 CLK 和 SYSREF 接口、交流耦合电容器靠近 DAC。 但是、在评估板中、它们靠近 CLK IC 放置。 请告诉我哪种配置是正确的吗?

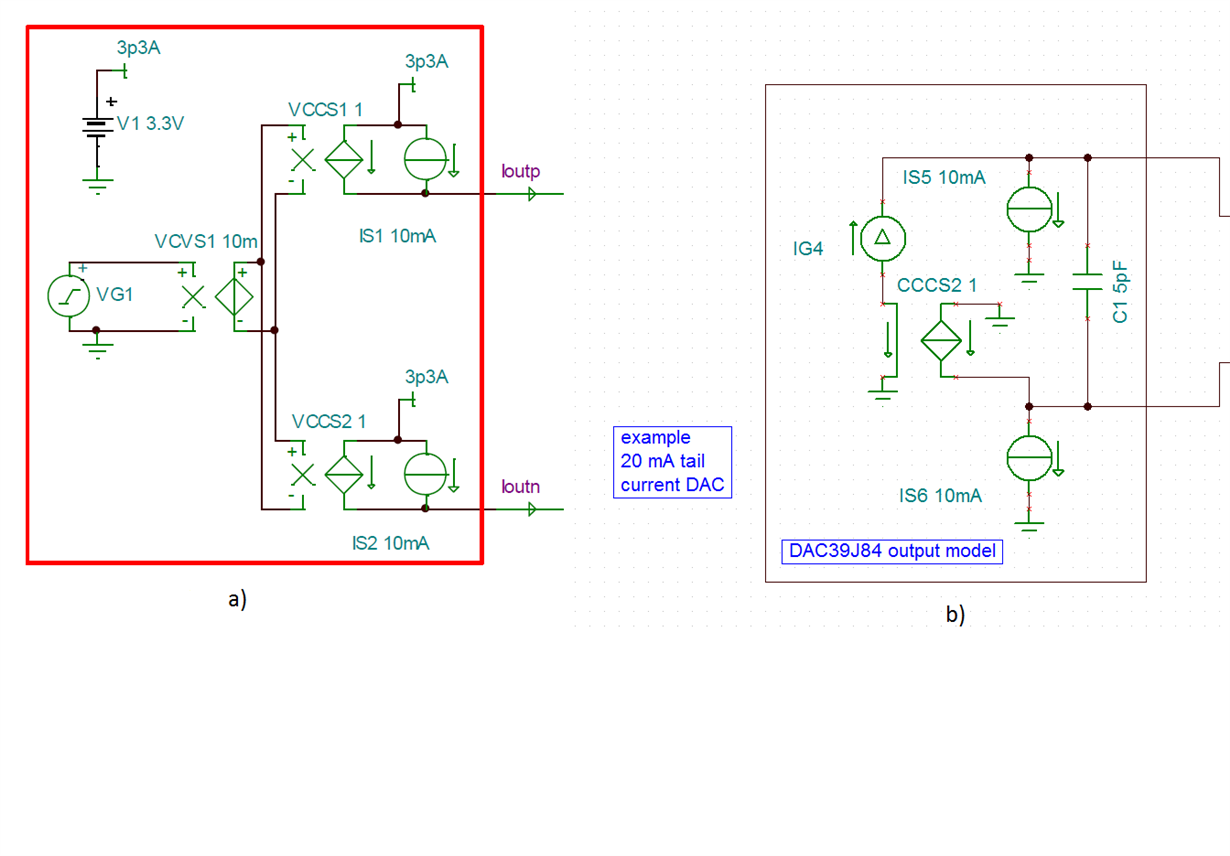

2-我对 DAC39J84的理解是它是一个电流源,因此我使用图(a)中的模型在 TINA 中对它进行建模,该模型是否正确? 我问这个原因我最近发布了一个关于 DAC39J84输出接口的问题 ,作为答案,我得到了图(b)作为它的模型。 感谢您在此处提供帮助、并与我确认图(a)中显示的模型是正确的。

此致

Samaneh