主题中讨论的其他器件: DAC38RF89

您好!

我们在 Xilinx FPGA (UltraScale 器件)上实现了一个 JESD204B 主器件。

在 FPGA 配置中、M=2、L=8 (LMFS)。

8个串行器/解串器通道连接到 DAC38RF82。

我们有一个16位/2.5Gbps 模式、在该模式下、四个通道连接到 DAC38RF82中的 DAC A、四个通道连接到 DAC B (Oe_DAC_ONLY = 0、Oe_LINK_ONLY = 1)。

物理连接如下所示:

FPGA DAC38RF82

TX0 RX1

TX1 RX4

TX2 RX6

TX3 RX7

TX4 RX5

TX5 RX0

TX6 RX2

Tx7 RX3

对于 TX0、TX2、TX5、TX7、极性应反转(在 DAC 中)。

我们用于16位/2.5Gsps 的 JESD 模式为 LMFSHd=82121。

在 FPGA 中、TX0使用通道 ID=0、TX1使用通道 ID=1、以此类推 TXN 的其余部分。

FPGA TX0-TX3路由到器件的 DAC A (通过横线、通道使能等)。

FPGA TX4-TX7路由到器件的 DAC B。

我的问题:

- 使用表9、DAC38RF82和 DAC38RF89的 JESD204B 格式(数据表中的第30页):

我们在最后一个表条目(41121/82121)中使用该模式。

我们需要的模式似乎是2 TX、82121。

1 TX 和2 TX 之间的区别是什么? (我们使用 one_dac_only=0、one_link_only=1)。 - 使用表41、针对 JESD 和插值模式的寄存器编程(数据表中的第52页):

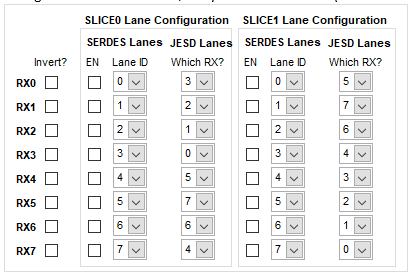

哪种模式是我们正确的模式:82121/nA 或41121/82121? - 提供上述信息、您能填充随附的(来自 DAC38RFxx EVM GUI):

(或提供相关寄存器设置)

谢谢!

吉尔·赫尔希曼