主题中讨论的其他器件:LMK04828、 LMX2582、 LMX2592

您好!

我们在设计中使用三个 DAC38RF80。 对于计时、我们使用 LMK04828、LMX2582/92和 HMC987。

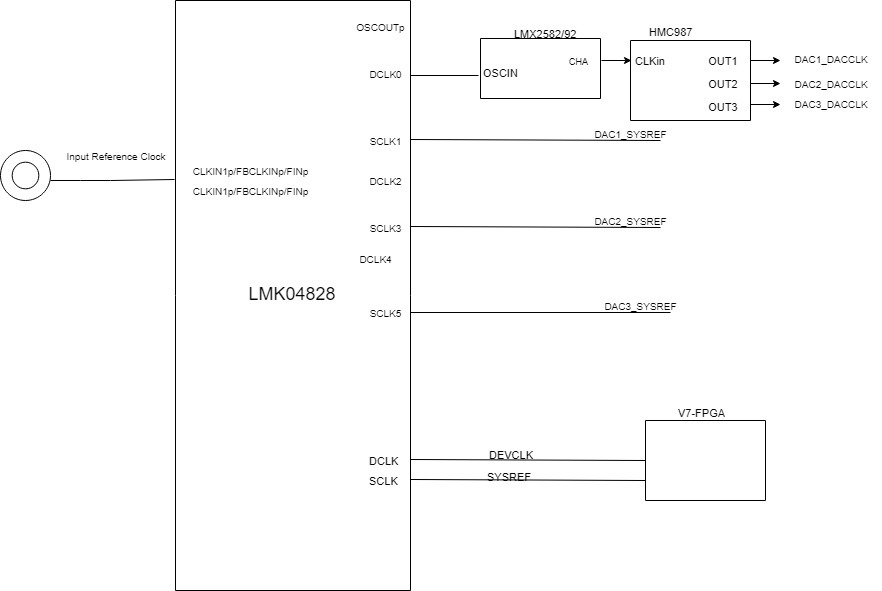

时钟树如下所示:

LMK04828的一个输出连接到 LMX2582/92的 REFCLK 输入。 LMX 的通道 A 连接到缓冲器 HMC987、后者用于缓冲输入、然后 HMC987的三个输出连接到三个 DAC 的 DACCLK 输入。

用于同步的 SYSREF 时钟由 LMK04828提供。

尽管 DAC 具有内部 PLL、我们可以直接馈入 LMK04828中三个 DAC 的 DACCLK 输入、如下所示、但 DAC38RF80的数据表中写入的内容是、为了实现 DAC38RF80的最佳性能、请在 PLL 旁路模式下使用 DAC:

我的问题是:

在噪声和同步情况下、上述两个方框图中的哪种配置都能提供最佳性能? 我们将使用最大采样频率为9GSPS 的 DAC。

2.当我们使用 DAC 的内部 PLL 作为 DAC PLL 的基准时、DAC 性能是否会有任何差异 ;使用 LMK04828输出作为 DAC PLL 的基准;使用 DAC 作为 PLL 旁路模式;使用 LMX2592输出作为 DAC 的采样时钟。 LMX2592本身从 LMK04828接收其基准。

我们将非常感谢尽早作出反应。

谢谢、

Lalit