大家好、我使用的是评估套件、其中 FPGA 以有线方式作为主器件、但由于 ADC 在第一个 DRDY 下降沿未向我提供数据、因此遇到了一些问题。 然后、我看不到 DRDY 恢复为低电平、因此我想知道我是否在以下位置设置不正确:

对于具有+/-2.5V 输入电压的异步中断模式、我具有以下设置:

JP1:已安装、以允许 FPGA 成为主器件

我使用的是 USB 电源、因此将 JP2和 JP3跳线保持原样

JP5:1-2: (M0:IOVdd 异步中断模式)

JP6:2-3 (M1:GND 24位)

JP7:我尝试了2-3和浮点并获得了相同的结果。 (禁用 M2汉明码)

JP8:未安装(的电荷泵)

JP9:已尝试安装和卸载。 (使用板载参考)

JP10:未安装(使用板载 IOVDD)

JP11:2-3 (使用+/-2.5V 电源)

我使用以下配置过程来启用 ADC 的4096过采样、以便在异步中断模式下提供4kHz 的采样率。 如果 CFG 中的设置不正确、请告诉我:

发送空命令:0x000000

发送解锁命令:0x065500

发送 SYS_CFG_REG 写入:0x4B6800

发送 CLK1_REG 写入:0x4D0000

发送 CLK2_REG 写入:0x4D0000

发送 ADC_EN 寄存器写入:0x4F0F00

发送唤醒命令:0x003300

发送锁定寄存器命令:0x055500

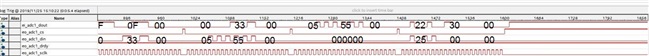

发送空命令:0x000000 (我在这里得到的每个响应都是正确的、您可以在逻辑分析器快照中看到它)

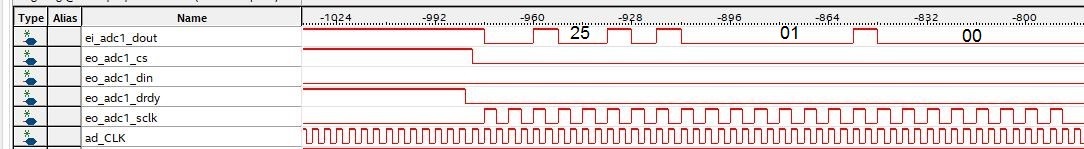

等待 ADC 将 DRDY 拉至低电平、然后继续并读取所有通道数据。 当我读取数据时、我将锁定寄存器命令返回为4个数据通道的状态、但平坦 DIN。 当我保持 ADC 不变并复位 FPGA 以重新启动初始化例程时、我只有在 DRDY 变为低电平后才能看到来自 ADC 的正确数据。 然后、读取该值后、我不会看到 DRDY 再次变为低电平。

这是初始化:

这是首次读取的数据: