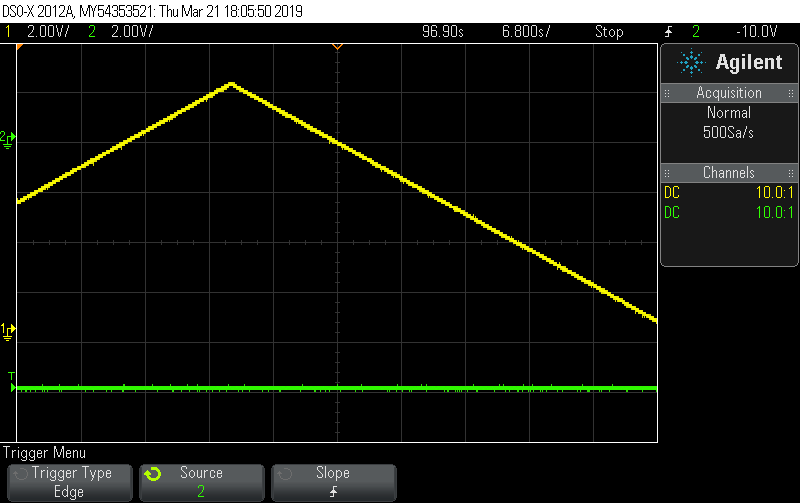

大家好。 我使用的是 DAC7821、这是 一款连接到 Infineon XMC4800微控制器的12位并行 DAC。 我将其用作0V 至10V 范围内的单极输出。 如果我将 DAC 代码写入 DAC 数据寄存器输出正确。 但是,如果我向寄存器输出(9.98*409.6)写入,则 Put 为零。 因此最大输出为9.97。

但根据我的理解、您可以为 DAC 提供的最大数字输入为1111111111、对应于 FFF。 但在我的例子中、如果我给出9.98、则相应的数字代码 位将是1111110111、低于最大范围。 我是否理解正确??