主题中讨论的其他器件: ADS5294EVM、 ADS5294

您好!

我尝试将 ADS5294EVM 与 TSW1400EVM 配合使用、并且遇到了一个奇怪的问题。 我有 TI 的 Quartus 项目文件、它编译得很好。 我尝试的是转换为 VHDL 并稍微简化代码。 所有 PLL 和串行器/解串器的设置方式与 TI 的固件完全相同。 来自 ADC 板的 DCLK (数据时钟)进入引脚 AA7和 AA6、这个驱动一个 PLL、而 PLL 的输出时钟(2*DCLK)驱动 SerDes 输入。 当我尝试编译代码时、我收到以下错误

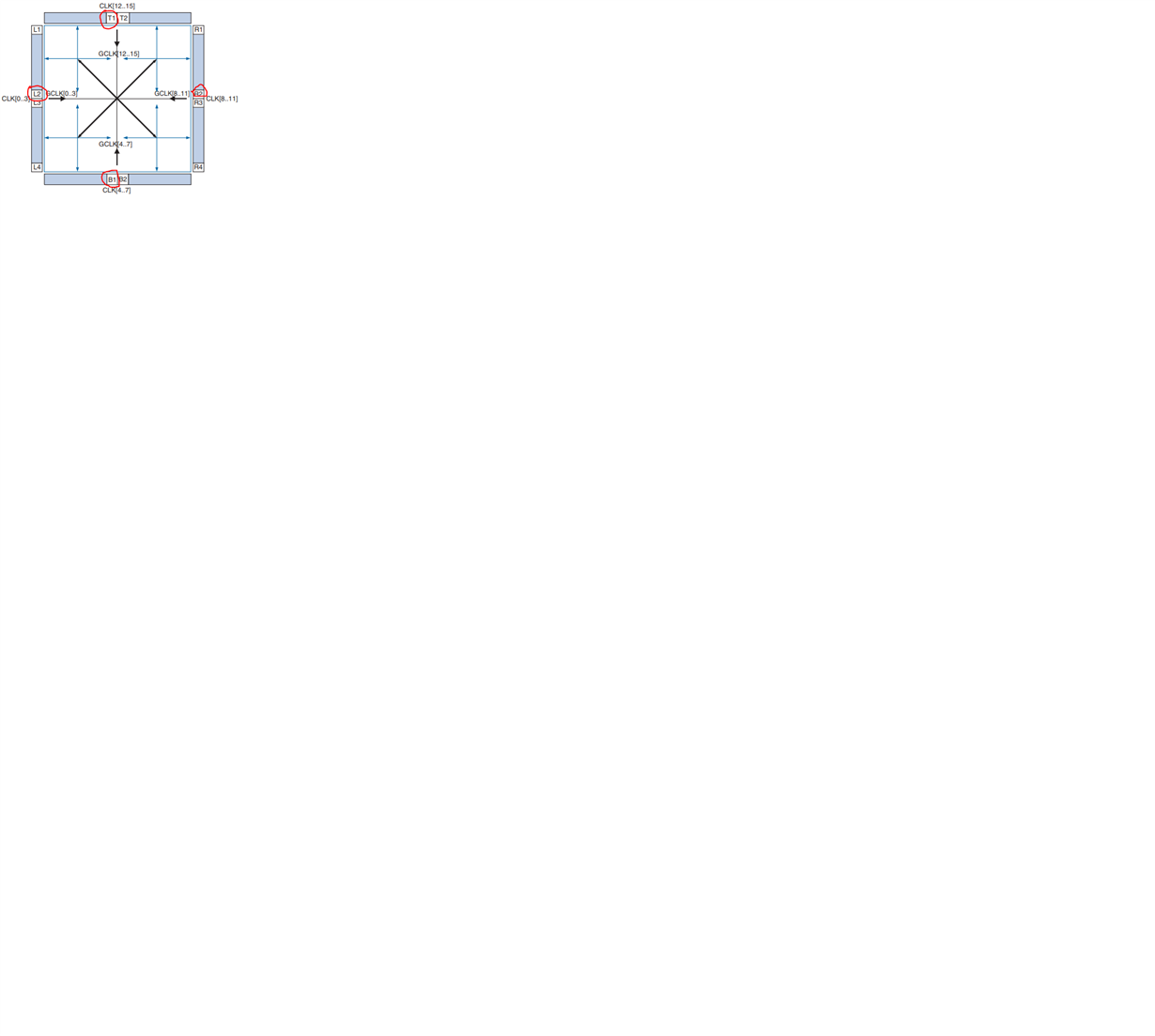

错误(176562):无法在 PLL 位置 PLL_B1中放置左/右 PLL "PLL_ADC_DATA_ACQ:inst24|altpll0:ADC_PLL_CONFIG|altpll:altpll_component|altpll0_altpll2:auto_generated|pll1"、因为该位置不接受左/右 PLL

错误(176563):无法在 PLL 位置 PLL_L2中放置左/右 PLL "PLL_ADC_DATA_ACQ:inst24|altpll0:ADC_PLL_CONFIG|altpll:altpll_component|altpll0_altpll2:auto_generated|pll1"、因为 PLL 的位置与 PLL 中的分配位置不兼容

错误(176161):无法将输入时钟引脚 clk_LVDS_rx0_p 置于驱动快速 PLL PLL_ADC_DATA_ACQ:inst24|altpll0:ADC_PLL_CONFIG|altpll:altpll_component|altpll0_altpll2:auto_generated|pll1置于非补偿性 PLL7模式下-至少一个非补偿性 PLA-DAL7驱动器/非快速位置

错误(176562):无法在 PLL 位置 PLL_T1中放置左/右 PLL "PLL_ADC_DATA_ACQ:inst24|altpll0:ADC_PLL_CONFIG|altpll:altpll_component|altpll0_altpll2:auto_generated|pll1"、因为该位置不接受左/右 PLL

不知道为什么我遇到这个问题、因为我使用的是与 TI 固件完全相同的东西。 固件团队的某个人能否仔细研究一下、如果我需要在某个地方添加任何限制、以便它不会给编译带来错误、请告诉我。

提前感谢

此致、

Ramakrishna