如何获得方波信号?

我对写入寄存器的内容感到困惑

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我是否可以问您是否碰巧拥有/使用 ADS1298R 评估套件/板(EVM)?

您能不能看一下 EVM 用户指南

"4.2内部测试信号输入配置寄存器2控制内部生成的方波测试信号的信号幅值和频率。 该测试信号的主要目的是验证前端多路复用器、PGA 和 ADC 的功能。 可以在 ECG Display (ECG 显示)选项卡上查看测试信号、如图31所示。 有关使用 ECG 显示选项卡的详细说明、请参阅第3.5.5节。"

看看 您所指的方波是不是这样的?

谢谢

您好!

"据说、"此 SDATAC 操作码命令取消连续读取数据(RDATAC)模式。 "。 我认为该命令要求 ADC 停止转换。 DRDY 将保持高电平。"

是的。 没错。

是否只发送一次 SDATAC 操作码命令?

"CLKSEL 连接到 DVDD、并且在 ADC 加电时将 START 拉至高电平。"

CLKSEL=1表示使用内部时钟。

什么是 RESP_CTRL[1:0]设置? 请注意- (1)如果 CLKSEL = 1 (内部主时钟)、请勿设置 RESP_CTRL[1:0]= 11。

如果电路/硬件将 START 拉至高电平,请确保检查数据表“9.4.1.1启动模式下拉低 START 引脚至少2个 tCLK 周期,……” 开始转换。" 和 9.4.1.1.1稳定时间以及 9.4.1.2数据就绪引脚(DRDY)。

"如果 AVDD-AVSS = 2V、会发生什么情况? 在7.1中、AVDD-AVSS 的最小值为-0.3、但在7.3中、建议的最小值为2.7V。 如果 AVDD-AVSS = 1.57V、这是不可接受的? 为什么? "

AVDD-AVSS=1.57V 可能无法正常工作、因为它超出了建议的工作条件、因此、如果 使用方法不符合/不符合数据表要求、TI 将无法保证性能和性能。

7.1表示防止/避免损坏器件的范围;7.2表示器件正常工作/运行的范围。

现在、 您能否 正确读取 ID 寄存器的器件 ID?

复位引脚是如何连接的?

同时、请查看此主题、了解您是否需要调试 SPI 通信/对其进行故障排除。

检查并验证电压要求后、请尝试以下操作:

更改为较慢的数据速率设置。

是否可以尝试发送 RDATA 命令? 请看 9.5.2.4开始:开始转换和 9.5.2.8 RDATA:读取数据。

谢谢

是的、我只发送 SDATAC 一次。 DRDY 是否应保持高电平、或者即使存在脉冲也没关系?

我不确定 RESP_CTRL[1:0]。 我没有设置 RESP 寄存器。 我认为它保持默认值、 可能是00。

RESET 始终拉高。 读取11.1后、我在复位拉高之前添加一个延迟。 然后、RESET 被拉低一段时间、然后再次拉高。 我认为延迟符合最低要求。

然后我发送 SDATAC 和 RREG。 我更改了要读取的寄存器数量、但我获得的数据始终相同。

我再次检查了 AVDD-AVSS 和 DVDD。 DVDD = 2.5V、AVDD-AVSS = 3V。

您好!

感谢您检查 11.1加电排序、

是否可以通过示波器提供波形来查看加电序列是否与图105匹配?

您是否在 VCAP1引脚上有一个连接到 GND 的电容器?

您能否确认可以毫无问题地写回和读寄存器值? 例如

ID 寄存器的器件 ID 是否正确? 这是只读的

和

您能尝试在下面写读一下吗-

//激活(1mV V_ref/2.4)方波测试信号

//在所有通道上

SDATAC

WREG CONFIG2 0x10 //9.6.1.3 CONFIG2:配置寄存器2 (地址= 02h)

WREG CHnSET 0x05 //9.6.1.6 CHnSET:单个通道设置(n = 1至8)(地址= 05h 至0Ch)

RDATAC

//查找/DRDY 并发出24+n*24个 SCLK

如果您可以在上述步骤中成功进行读取和写入、则可能需要使用示波器在所有/DRDY 和 SPI 线路上进行探头

建议查看以下内容以进行信号和代码调试和/或故障排除:

谢谢

您好!

"SCLK 为110kHz"、即 tSCLK 的周期约为9090.90ns、有点慢、但可能还可以、这是 SCLK 相对于其他信号的重要性。

您是否将 SPI 设置设置设置为"注意:SPI 设置为 CPOL = 0和 CPHA = 1."?

您能否探测 /DRDY 和 SPI 线路并参考数据表图1。 检查以下各项-

写入寄存器时、/CS 是否在 SCLK 的第一个上升沿之前至少被拉至低电平的时间达到 tCSSC?

那么、在 SCLK 下降边沿之前、DIN 是否稳定(不改变)至少对于 TBIST?

确保 SCLK 下降沿和 DIN 的边沿不对齐/重叠。

确保在 SCLK 下降沿之后、DIN 不会在至少 tDIHD 秒内发生变化。

请按照相同的思路查看图1、并确保 DOUT 也符合第17页列出的时序限制/要求。

建议使用 EVM、以便您可以比较 EVM 和您的 EVM 之间的数字信号波形。

谢谢

是的、我将 SPI 设置为 CPOL=1和 CPHA=1。

在写入寄存 器之前、如果我想读取 ID 寄存器、我得到0x00 0x00 0xd2 0x06 0x00 0x40、然后读取以下三个寄存器。

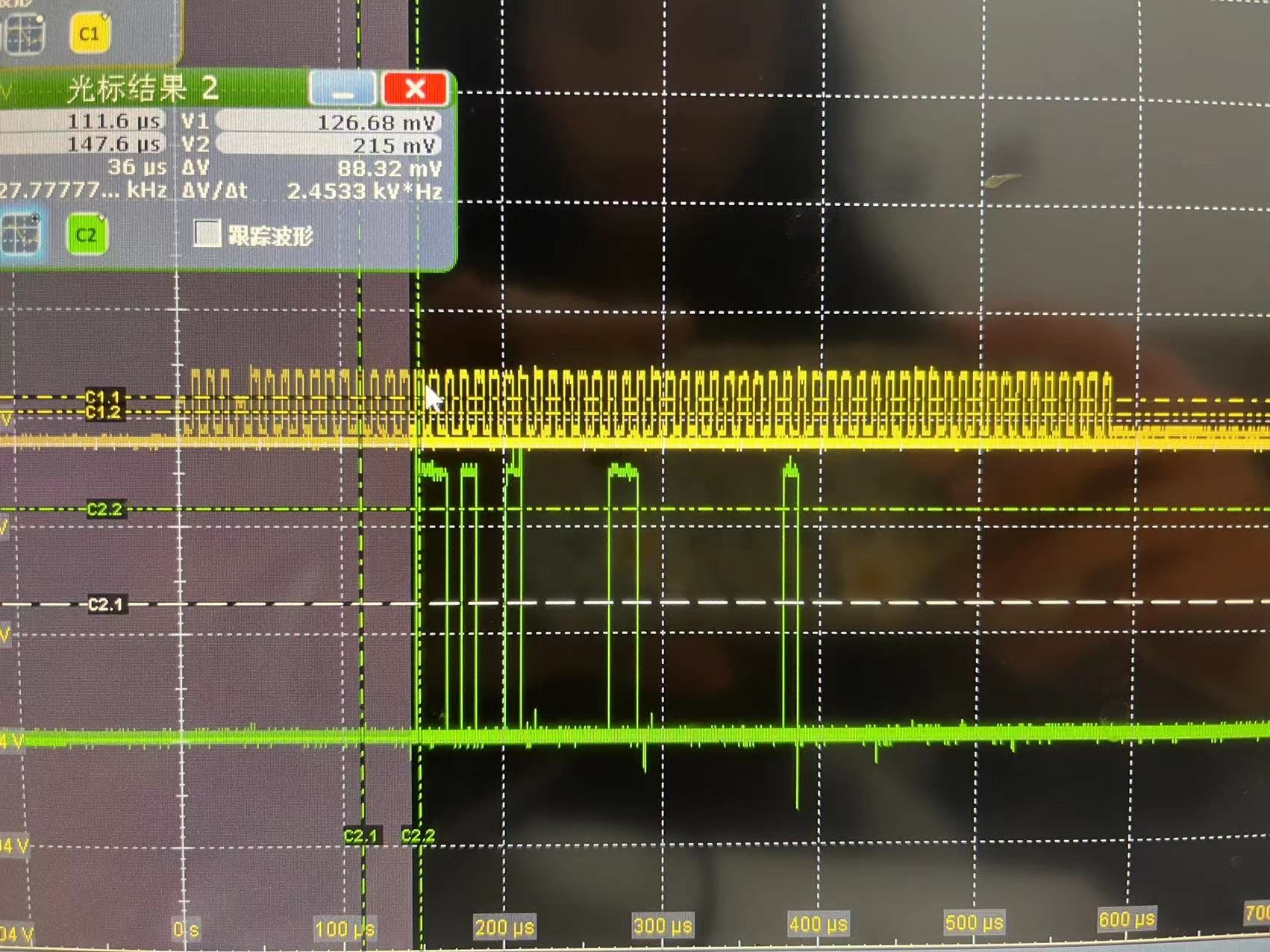

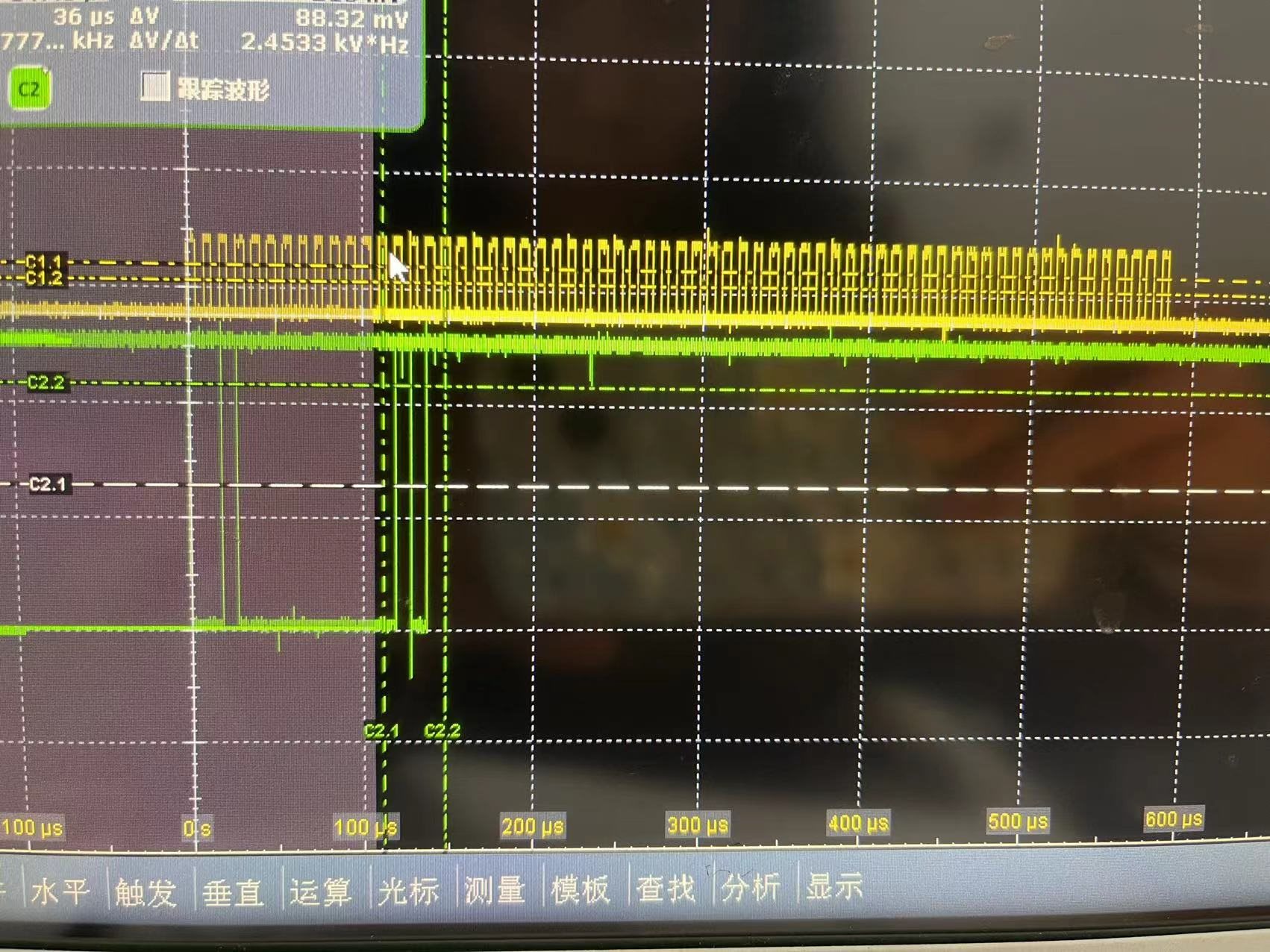

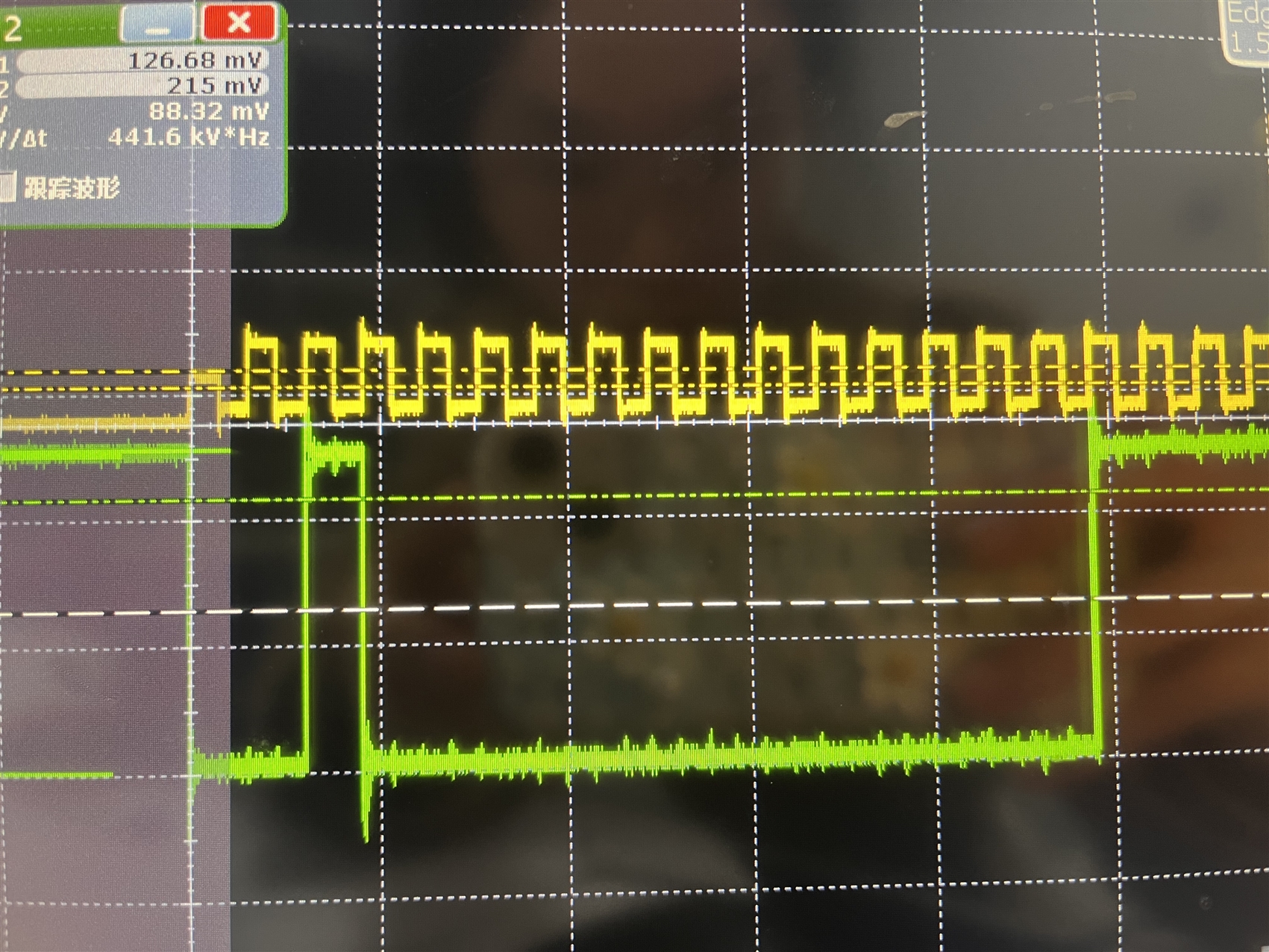

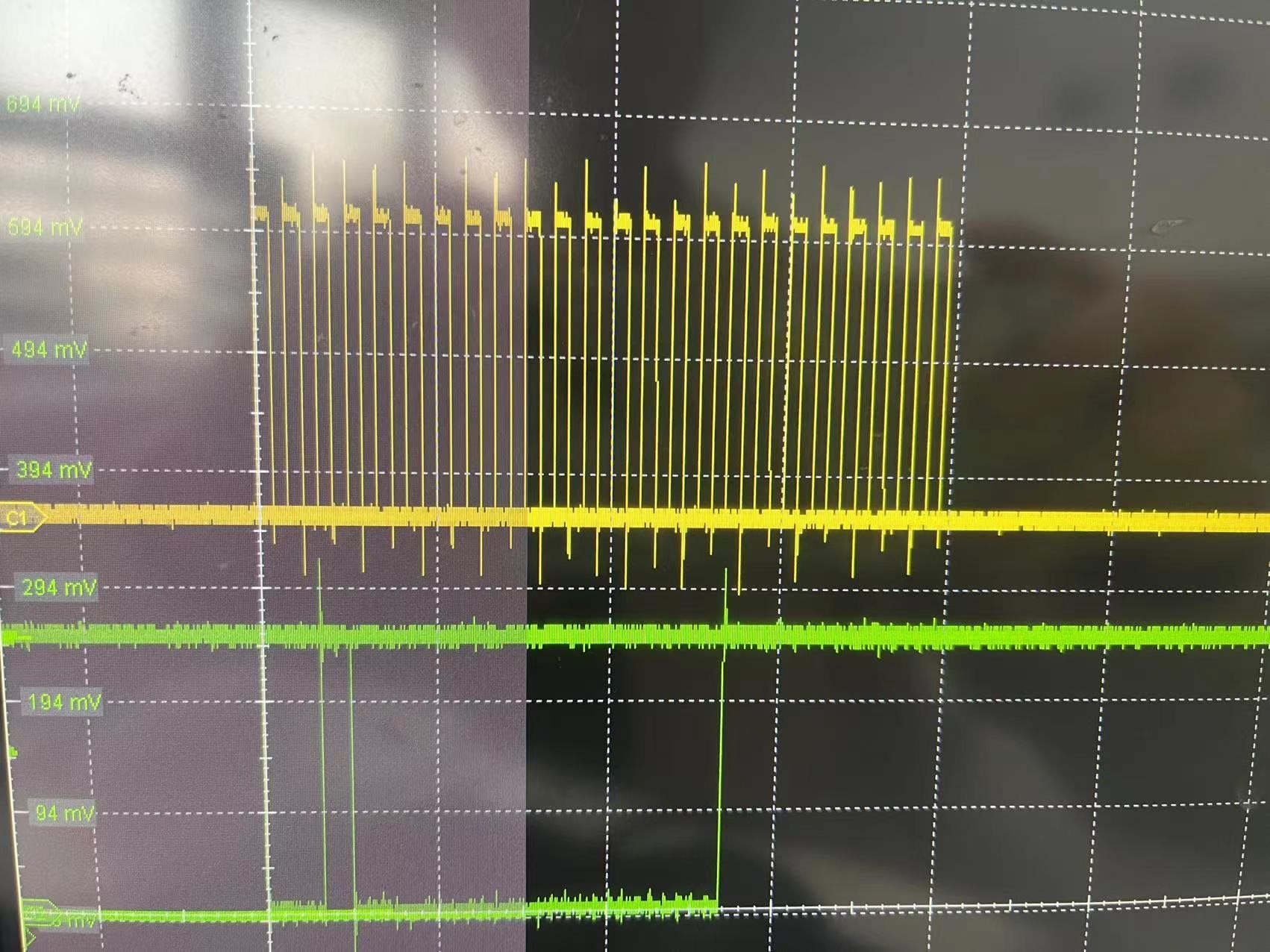

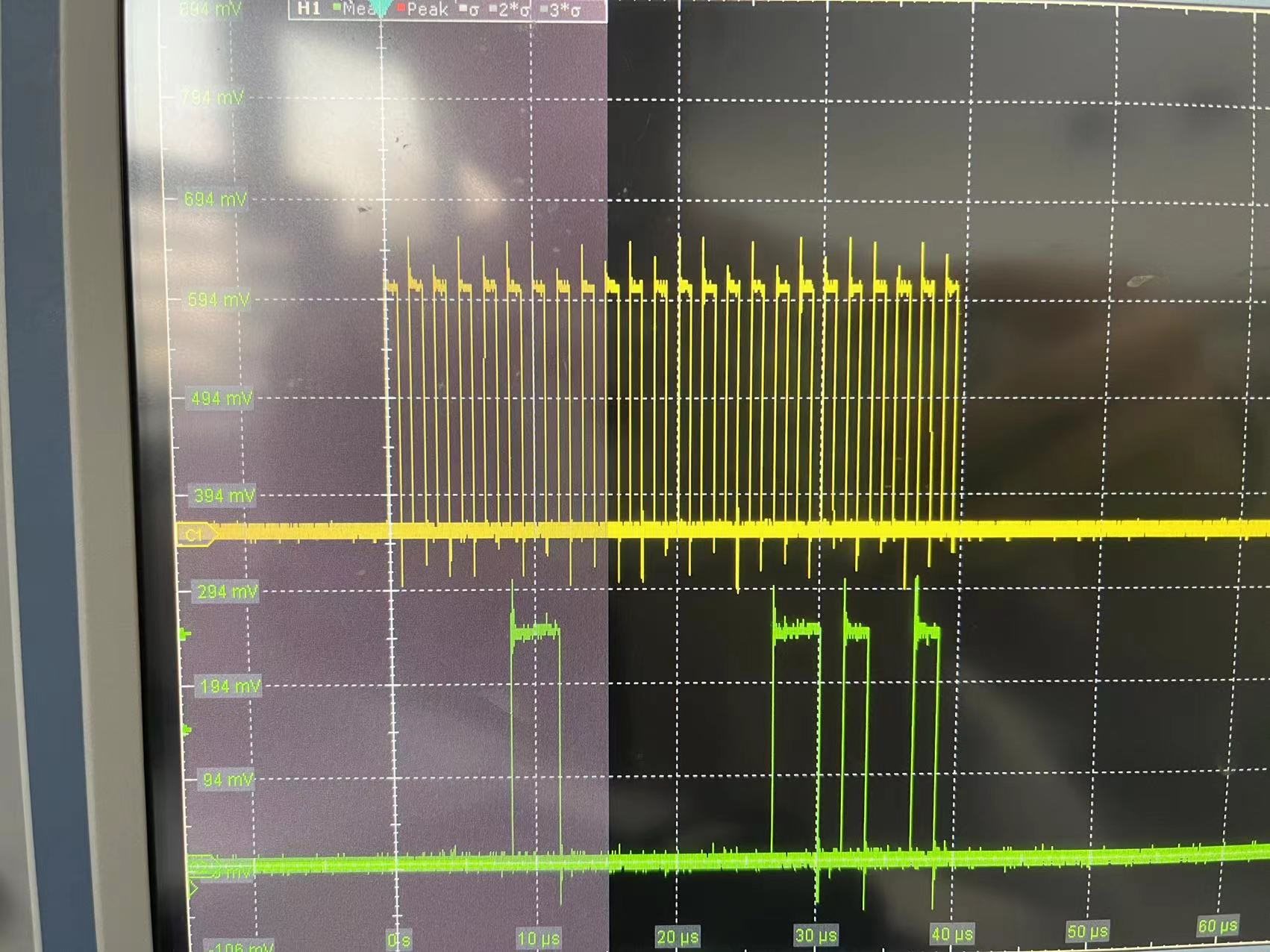

这就是我得到的。 ADC1298r 的 DOUT。 黄线为 SCLK。 绿线是 ADC1298r 的 DOUT。

然后我发送 WREG、将 0x41 (WREG) 0x0C (number) 0xC4 (config1) 0x31 (CONFIG2) 0x40 (CONFIG3) 0x00 (LOFF) 0x15 (CH1) 0x15 (CH2) 0x15 (CH3) 0x10 (CH4) 0x15 (CH5) 0x15 (CH6) 0x15 (CH7) 0x15 (CH7)写入 ADC (CH7 (CH7)

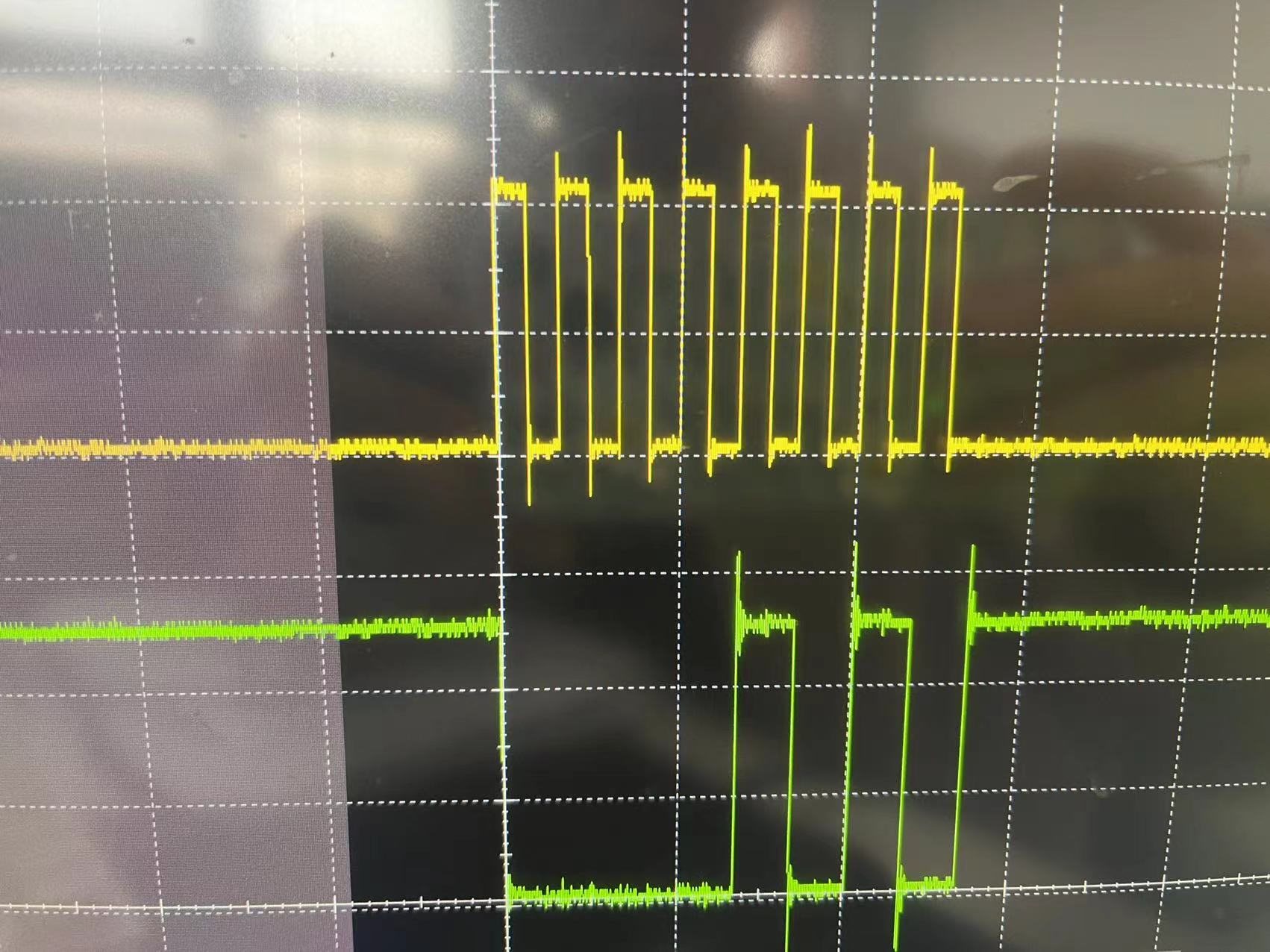

下图是 WREG 命令的一部分。 我认为 DIN 在 SCLK 下降期间是稳定的、AD 如下图所示。

然后、我按如下方式发送 RREG。 黄线为 SCLK、绿线为 DIN。

但 ADC 的 DOUT 会一直变化。 绿线是 DOUT、黄线是 SCLK。

您好!

感谢您的照片。

您能否在 SCLK 下降沿之前检查(放大)至少 TBIST 的 DIN 稳定(未改变)?

确保 SCLK 下降沿和 DIN 的边沿不对齐/重叠。

"在写入寄存器之前、如果我想读取 ID 寄存器、我得到0x00 0x00 0xd2 0x06 0x00 0x40 "

那么、从示波器来看、由 SCLK 计时的 DOUT 信号是否与您对 ID 寄存器的预期相匹配?

"但 ADC 的 DOUT 始终在变化。 绿线为 DOUT、黄线为 SCLK。'

在此期间、您是否向 DIN 发送任何命令? 起始 引脚设置/连接了什么?

您的通道设置/配置是什么? 您是否将其配置为读取测试信号?

DOUT 即使对于稳定信号也有轻微变化是有道理的、 LSB 可能会有一些波动/变化。 但是、您能否检查(放大)以查看 SCLK 的下降沿是否与 DOUT 的边沿不对齐/重叠。

您能否进行以下检查?

1.读取 9.6.1.1 ID:ID 控制寄存器(地址= 00h)、并确保示波器和主机均可根据数据表读取正确的值?

2.如果上述操作正常、请尝试读 写9.6.1.6 CHnSET: 单个通道设置(n = 1至8)(地址= 05h 至0Ch)(复位= 00h)、仅首先验证1个通道、例如通道1、在此期间、请观察范围以确保 SCLK 和 SPI 线路能够在正确的逻辑高电平和/或低电平上计时。

如果可能、请提供以上两个的图片(首选放大)。

谢谢。

我进行了一些测试。 还是错的。

首先、我将 RESET 拉至高电平。 大约25ms 后、我将 RESET 拉至低电平12.5ms。 然后、我再次将 RESET 拉至高电平。 25ms 后、我将 CS 拉至低 电平并发送 SDATAC。 然后、我开始定期发送 RREG 来读取 ID 寄存器。 SCLK 的时钟速率为655kHz。 START 引脚为0、从未改变。

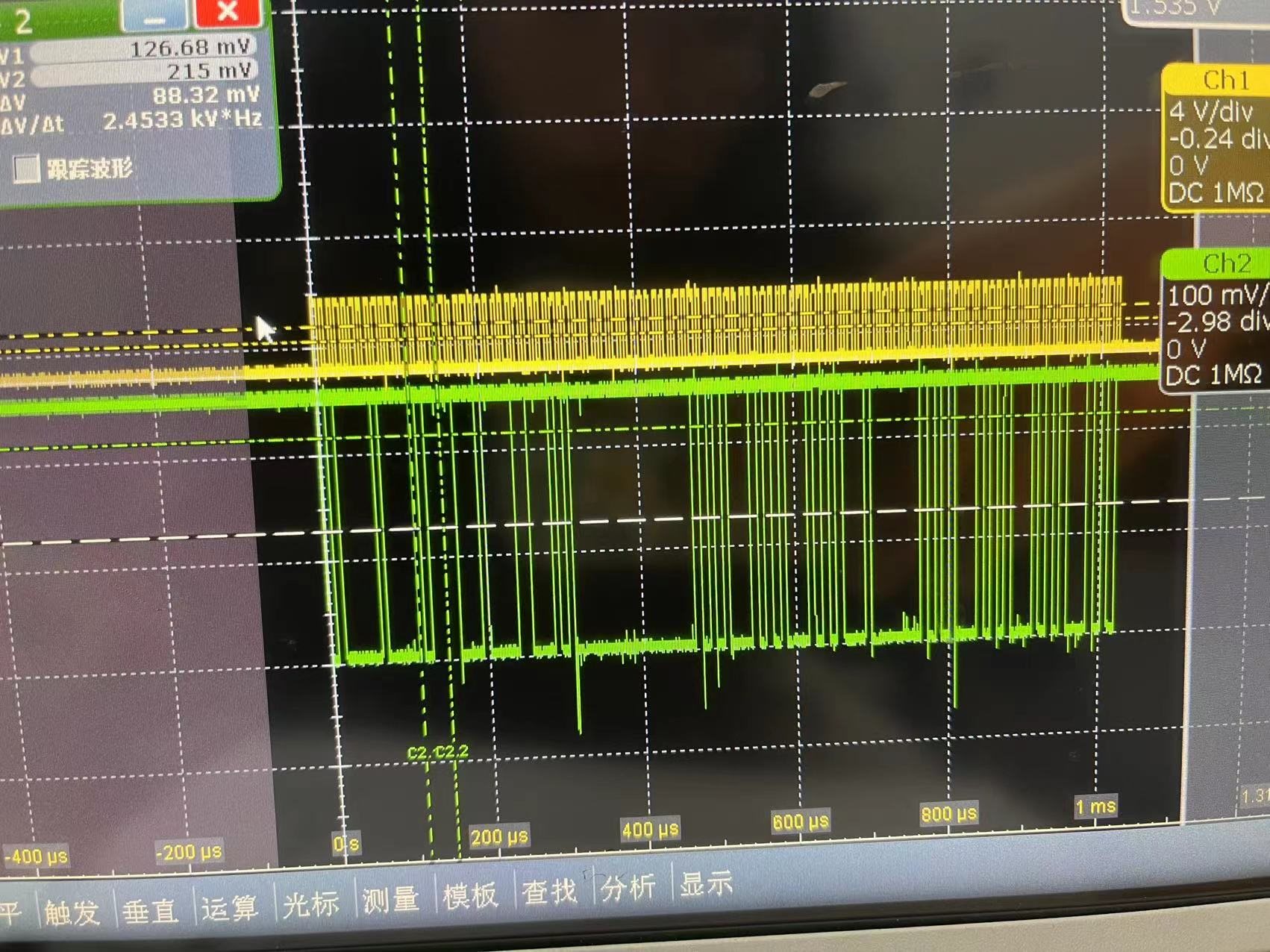

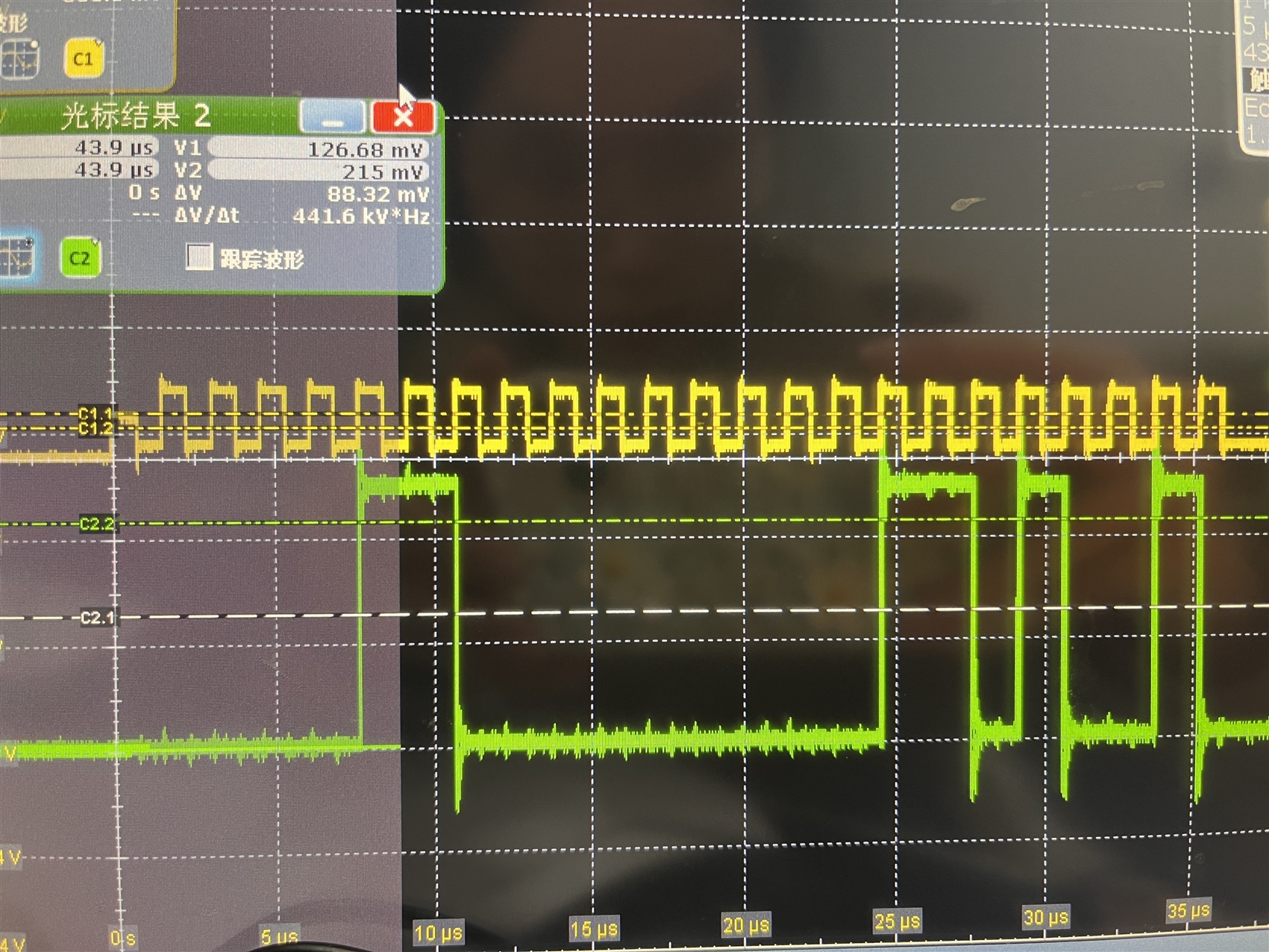

这是 DIN 和 SCLK。 我发送0x20 0x00 0xFF 来读取 ID 寄存器。

这是 DOUT 和 SCLK。 然后我得到0x06 0x00 0xd2。

我认为 DIN 和 DOUT 是稳定的。 这两个信号在下降沿不会改变。 RREG 命令每12.5ms 发出一次。 不应存在任何重叠。

这意味着"/如果 VCAP1 < 1.1V at t、请继续等待、直到 VCAP1 1.1V"出现在第 85页的数据表中?

VCAP1 - AGND =-300mV、VCAP1-AVSS= 1.2V。 它是否满足要求?

这 是有关其他引脚的统计信息。

AVDD-AGND = 1.5V、AGND-AVSS = 1.5V、AVDD-AVSS = 3V

DVDD-DGND = 2.5V AGND = DGND = 0

顺便说一下、 您能否在电路板上再次检查是否没有其他与 ADS 内部时钟发生冲突/竞争的振荡器时钟?

对于、"25ms 后、我将 CS 拉至低 电平并发送 SDATAC。 然后、我开始定期发送 RREG 来读取 ID 寄存器。 SCLK 的时钟速率为655kHz。 START 引脚为0、从未改变。"

您能否向我展示示波器信号的外观

SDATAC 停止读取数据连续模式0001 0001 (11h)

和

您是否也可以尝试发送

停止转换0000 1010 (0Ah)?

它们是否按 DIN 正确计时?

"然后、我开始定期发送 RREG 来读取 ID 寄存器。 "

那么、您是否在示波器上看到正确的 ID 寄存器值? 请参阅表17。 ID 控制寄存器字段说明

对于 ADS1298R、它可能为110 10 010 = D2h

然后、如果您的复位正确、请尝试查看 您是否可以在示波器上读取9.6.1.2 CONFIG1:配置寄存器1 (地址= 01h)(复位= 06h)。

如果上述两项操作都是正常的、那么请按照以下步骤尝试查看是否可以同时读取00h 和01h 寄存器(即与上面的两个寄存器相同)

图72。 RREG 命令示例:从寄存器00h (ID 寄存器)开始读取两个寄存器(操作码1 = 0010 0000、操作码2 = 0000 0001)

并观察这些值在示波器上是否看起来正确。

对于、"/如果 VCAP1 < 1.1V at t、请继续等待、直到 VCAP1 1.1V"(在 第85页)数据表中的值?

VCAP 需要充电至1.1V 才能正确允许/复位器件;请查看 图105。 上电时序图

因此、请确保电路板上的所有 VCAP 都符合数据表中的要求值

并确保在 将/RESET 拉至低电平至少2 tCLK 之前等待至少2^18的 tCLK、

即、如果您使用内部振荡器时钟、则为2.048MHz、因此 tCLK 大约为0.4883us、因此您可能需要等待至少1288005us、然后再将/RESET 拉至低电平。

如果上述所有操作都正确、则尝试在 示波器上读取9.6.1.3 CONFIG2:配置寄存器2 (地址= 02h)(复位= 40h)、以查看示波器上的复位值是否看起来正确。

然后、将1写入 02h[4]、即位4、然后读回寄存器值、观察范围。

您能否确保首先完成所有工作、然后我们继续

9.6.1.6 CHnSET:单个通道设置(n = 1至8)(地址= 05h 至0Ch)(复位= 00h)、但仅一个通道(例如 Channe1 CH1SET)。

谢谢

谢谢

在将复位拉至低电平之前、我延迟了大约500ms。 然后、我将复位拉至低电平1ms。 然后将 RESET 拉至高电平。

1ms 后、我将 CS 拉至低电平并等待1ms。

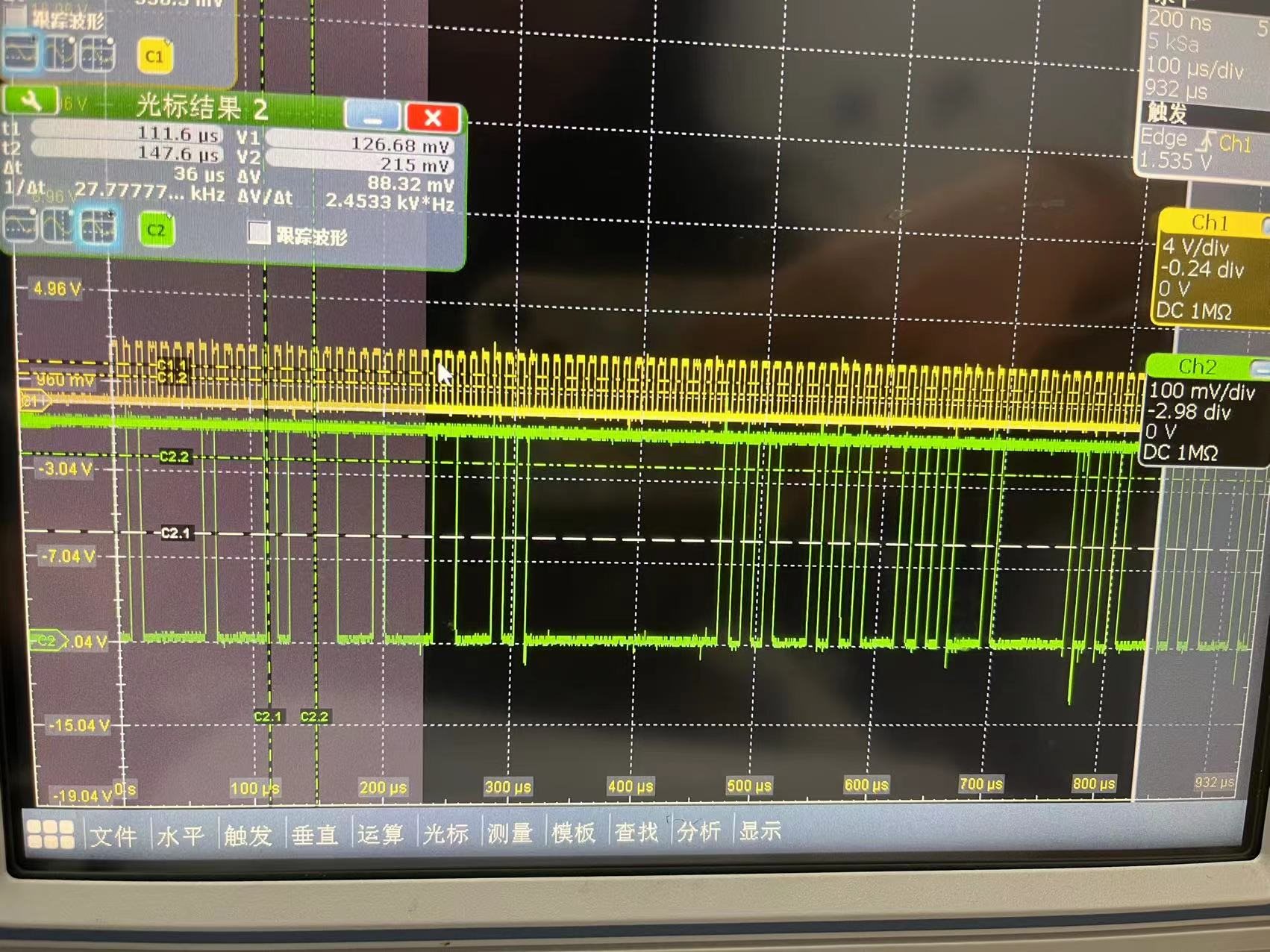

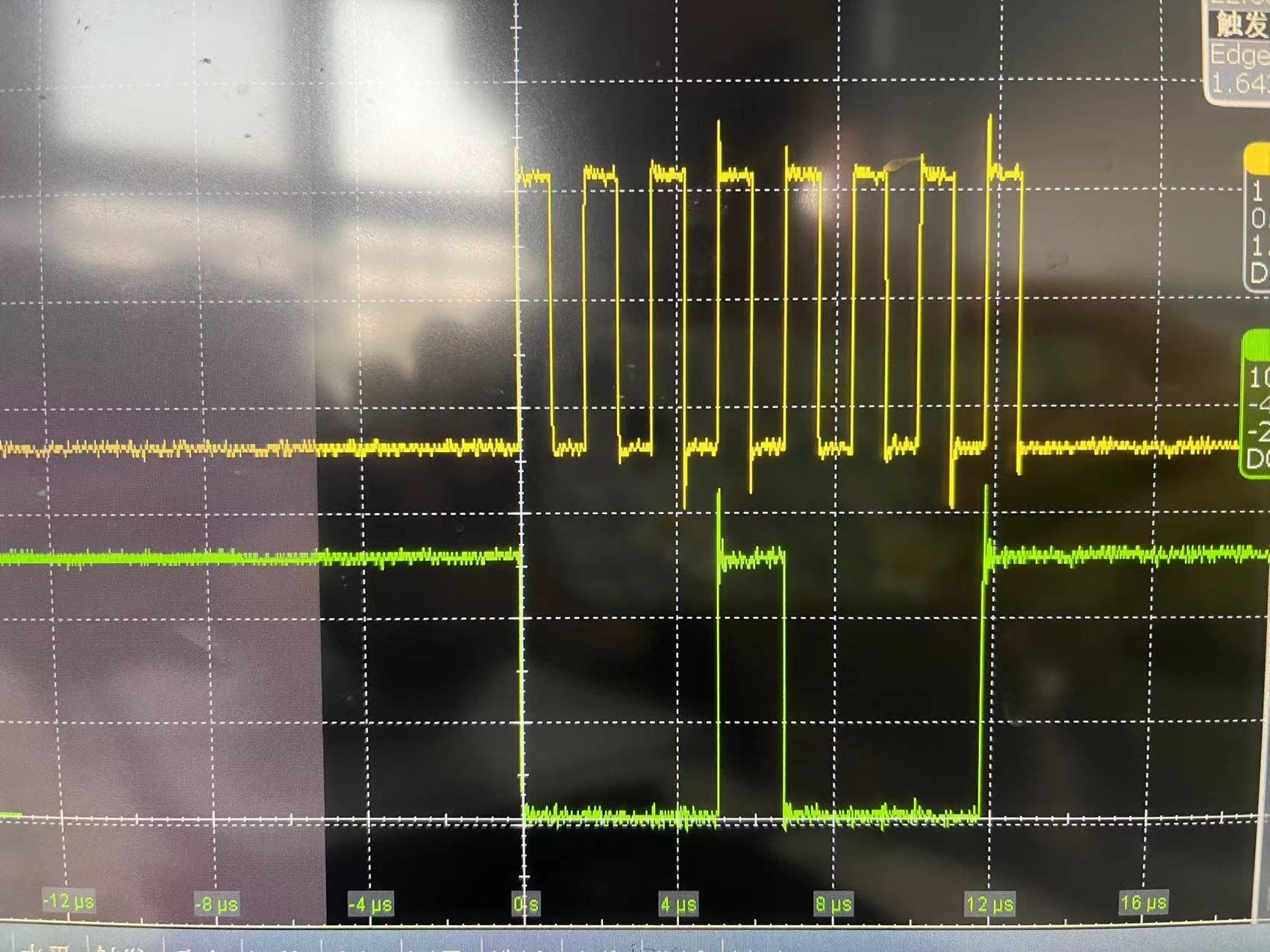

然后我发送 SDATAC。 绿线为 DIN 0x11

IThen 发送停止。 DIN 是绿线0xA。

然后、我发送 RREG 以仅读取 ID 寄存器。 这是 DIN 0x20 0x00 0xFF

DOUT 为0x06 0x00 0xD2

DOUT 始终从0x06开始。 我认为这仍然是错误的。

谢谢

您好!

有些问题没有得到解答-

1."顺便说一下、 您能否在电路板上仔细检查是否没有其他与 ADS 内部时钟发生冲突/竞争的振荡器时钟?"

SDATAC 停止读取数据持续模式0001 (11h)在 DIN 上看起来是正确的。

DIN 上的停止转换0000 1010 (0Ah)看起来正确。

2.请问您为什么在 "然后我发送 RREG 来只读取 ID 寄存器"中有/发送"0xFF"。 这是 DIN 0x20 0x00 0xFF"?

已了解 CLKSEL 连接到 DVDD、并且在 ADC 加电时将 START 拉至高电平。

那么、START 引脚是否由主机/主器件的数字信号控制?

4. START 引脚是否有连接 DVDD 的上拉电阻器、以及信号线是否连接/连接到主器件/主机的数字线路之一?

5. CS 引脚是否有连接到 DVDD 的上拉电阻器以及信号线路是否连接/连接到主设备/主机的数字线路之一?

6.复位前和复位后、是否可以将 START 引脚拉至低电平并保持 START 引脚为低电平?

因为、当 START 引脚为高电平或发送 START 命令时、A/D 转换开始、ADS 的/DRDY 将保持脉冲/触发状态。

目前、我可能建议将 START 引脚保持在低电平、并且仅使用命令来启动和/或停止。

7.如果您尝试只读取 9.6.1.1 ID:ID 控制寄存器(地址= 00h);请参阅表17。 ID 控制寄存器字段说明、 您是否读取/获取 ADS1298R 的110 10 010 = D2h?

谢谢

请 允许我问、为什么您 在 "然后我发送 RREG 来只读取 ID 寄存器"中具有/发送"0xFF"。 这是 DIN 0x20 0x00 0xFF"?

没关系吗? 我认为无论第三个字节是什么、都无关紧要、因为数据表中没有提到它。

2.起始引脚

START 引脚与主机的 GPIO 相连并由主机控制。

START 引脚初始化为0。 在测试期间、它永远不会被拉高。

3. CS 引脚

CS 引脚与主机的 GPIO 相连并由主机控制。

CS 引脚初始化为1。 它在上电后被拉至低电平。

在将复位拉至低电平之前、我延迟了大约500ms。 然后、我将复位拉至低电平1ms。 然后将 RESET 拉至高电平。

1ms 后、我将 CS 拉至低电平并等待1ms。

之后 CS 保持低电平。

谢谢

1."顺便说一下、 您能否在电路板上仔细检查是否没有其他与 ADS 内部时钟发生冲突/竞争的振荡器时钟?"

2、 SCLK 仍在 ADS 中计时、这可能会导致一些意外的性能。

3."START 引脚初始化为0。 在测试期间、它永远不会被拉高。" 好的。

此外、请查看随附的 PDF、看看您是否可以验证/验证 WREG 命令是否正常工作、例如为内部测试信号进行配置。

然后、查看您是否可以尝试使用 START 命令和 RDATAC 命令。

e2e.ti.com/.../SPI-Communication-_1320_-for-Internal-Test-Signal.pdf

谢谢

您好!

正确/完整地发送 RREG 命令后、DOUT 的第一个字节应为 ID 寄存器值、即对于 ADS1298R、 DOUT 应为0xD2。

您可能需要检查 SCLK 是否在正确的计时和边沿计时。

请参阅所附 PDF 文件的第1部分

仅针对器件 ID 寄存器0x00h->0010_0000_0000_0000读取寄存器 RREG 对于 ADS1298R、DOUT 应返回1101_0010 = 0xD2

谢谢