主题中讨论的其他器件:ADS8902B、

你(们)好。

我们在其中一个设计中使用 ADS8902B ADC、并希望对 SDO 的时序进行一些澄清。

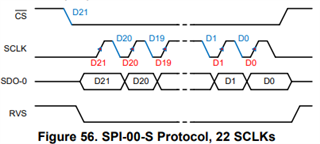

以下是 ADS8920B 数据表的屏幕截图:

(第11页)

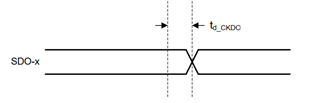

(第11页)

(第9页)

(第9页)

这意味着新数据将在 CLK 启动边沿之后的最后13ns 在 SDO 上准备就绪。

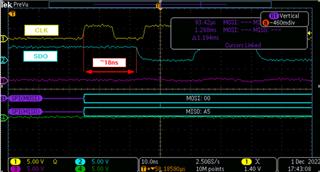

下面是在我们实现该 ADC 时捕获的跟踪、显示了 CLK 启动边沿后 SDO 上的数据准备就绪的接近18ns。 我们的主器件是一款 STM32F746IG、它要求数据在采样前5.5ns 在 MISO (来自 ADC 的 SDO)上有效。 因此、我们目前违反了该要求。 我们的 SCLK 为50MHz

我的问题是:

- ADS8920B 数据表中是否还提供了 TD_CKDO 的最小值和典型值? 我们正在考虑在 ADC 上使用早期数据启动(EDL)模式、该模式将使 SDO 提前10ns (1/2 CLK)。 如果 TD_CKDO 仅为7ns、EDL 是否会在启动边缘之前将 SDO 10ns 移动到3ns? 然后、主器件将读取先前的数据。

- 为什么 ADS8920B 需要18ns 才能在 SDO 上准备数据? 这似乎违反了最大值为13ns 的数据表规格。

此致、