主题中讨论的其他器件: ADS4245、 LMK61E2-100M

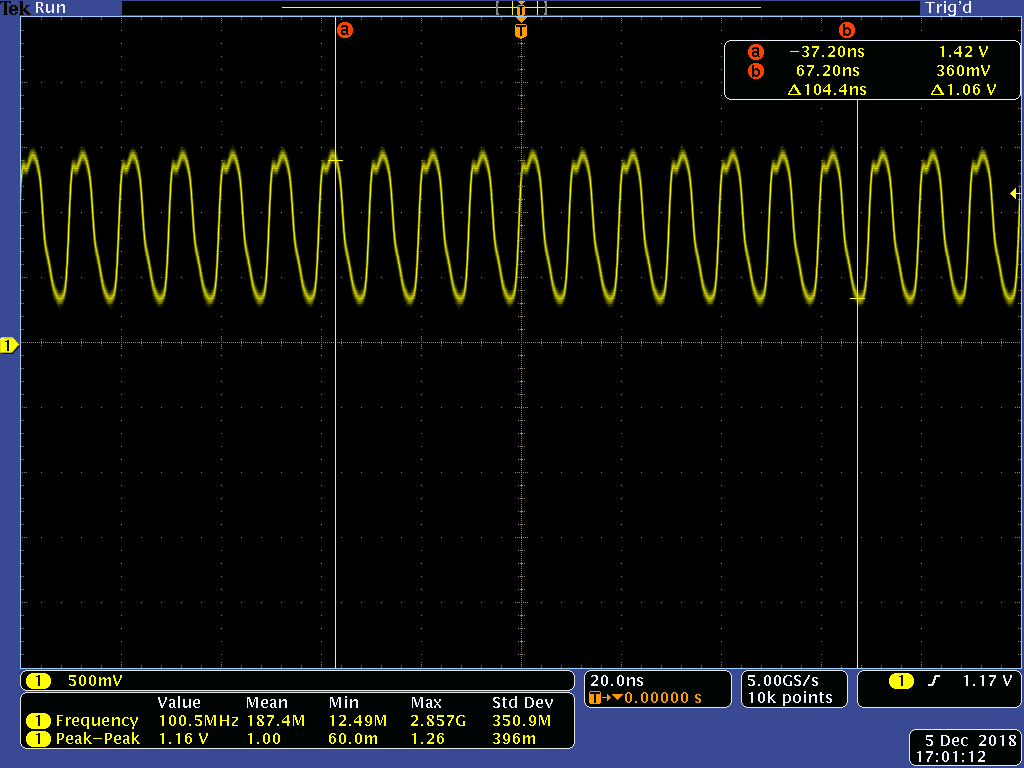

我们已使用 ADS4245-EP 组装了3块电路板。 这三个都正常工作。

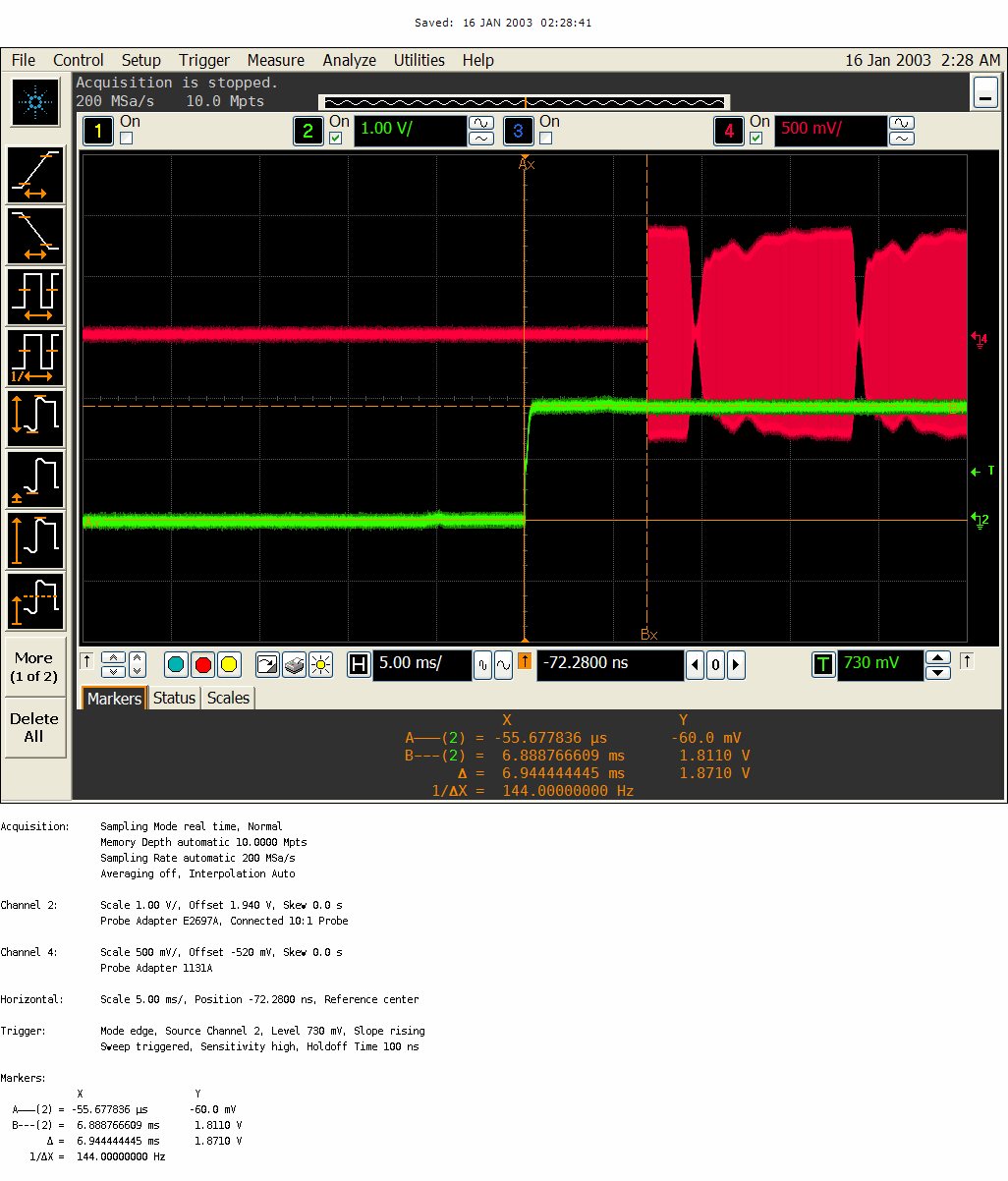

现在、当我们检查 ADC 数据在两个卡中不正确。

调试后、会注意到-

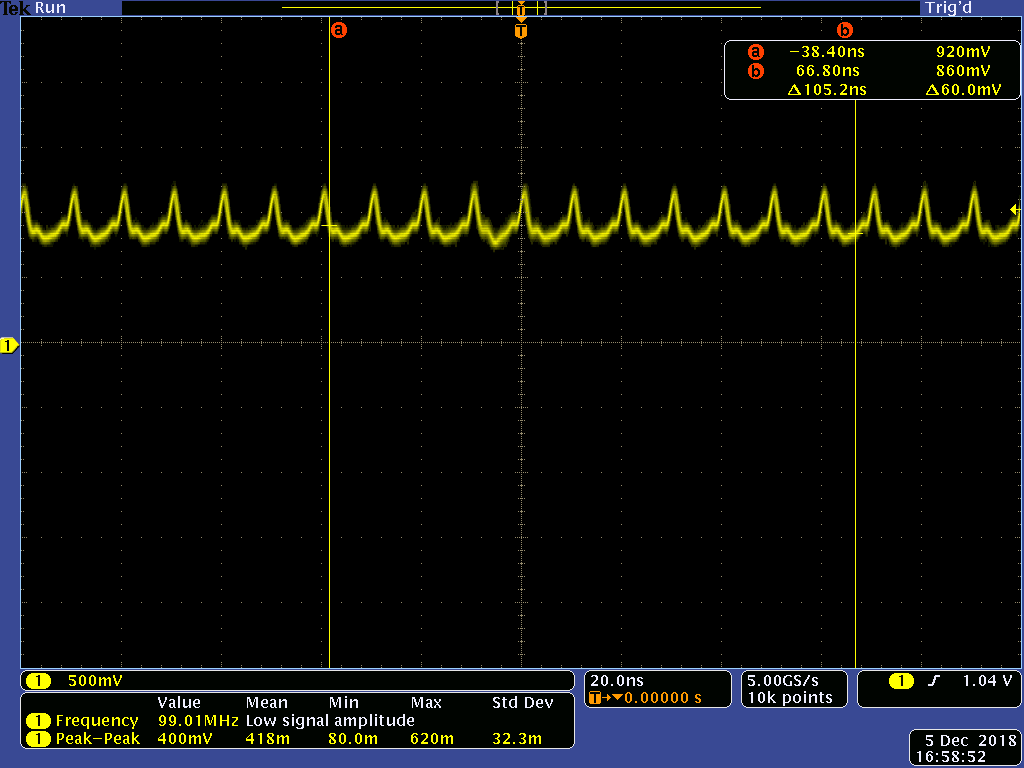

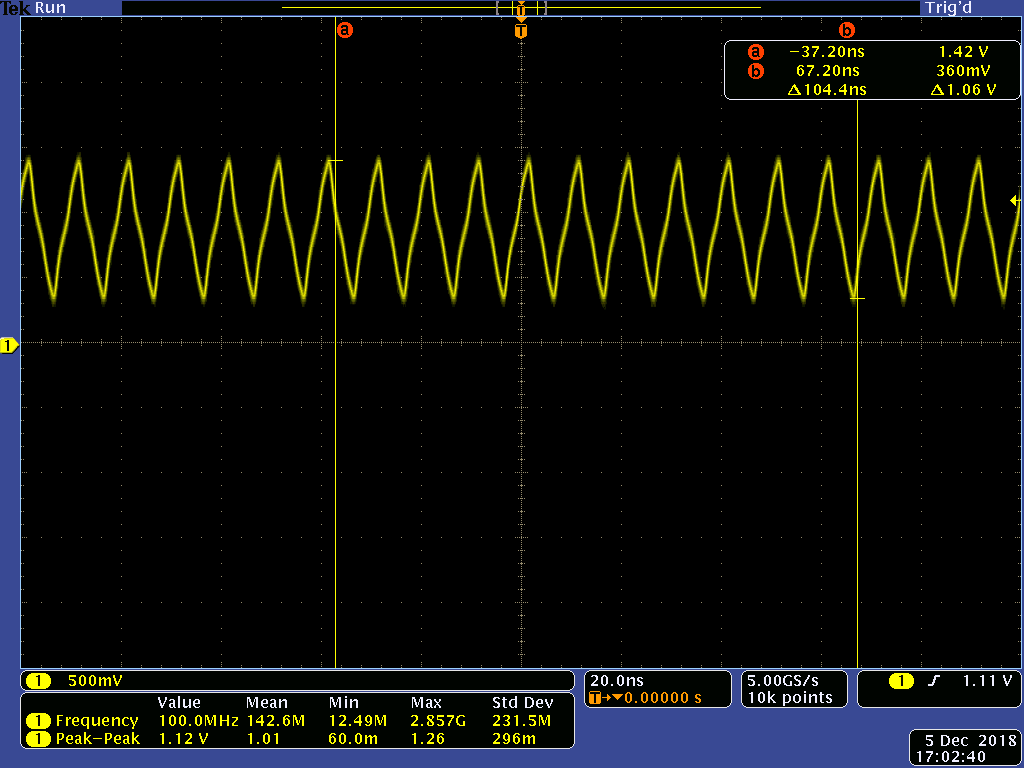

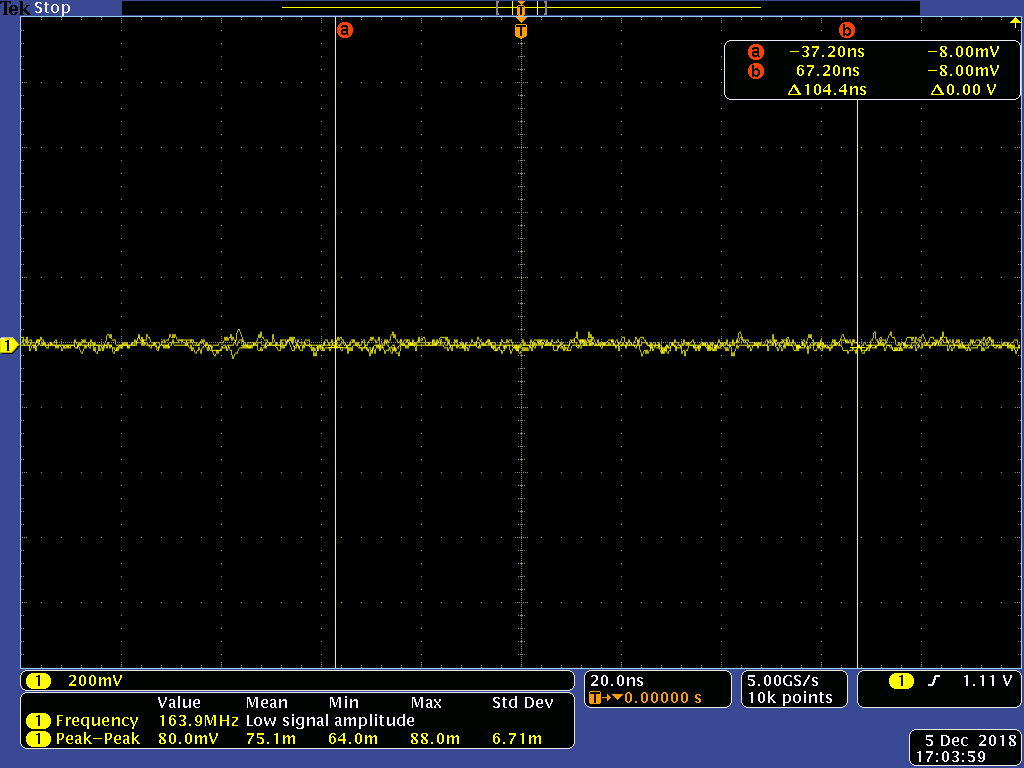

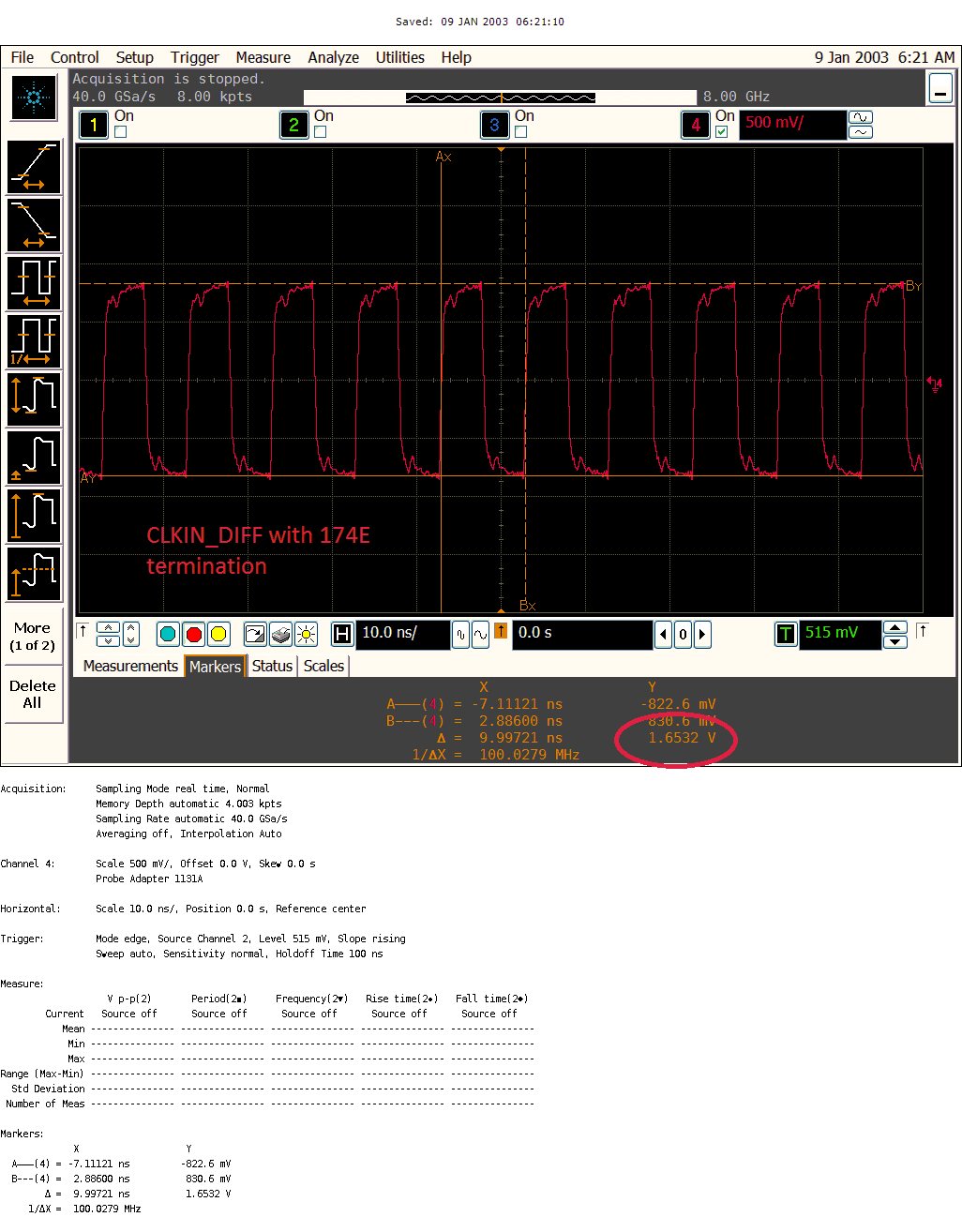

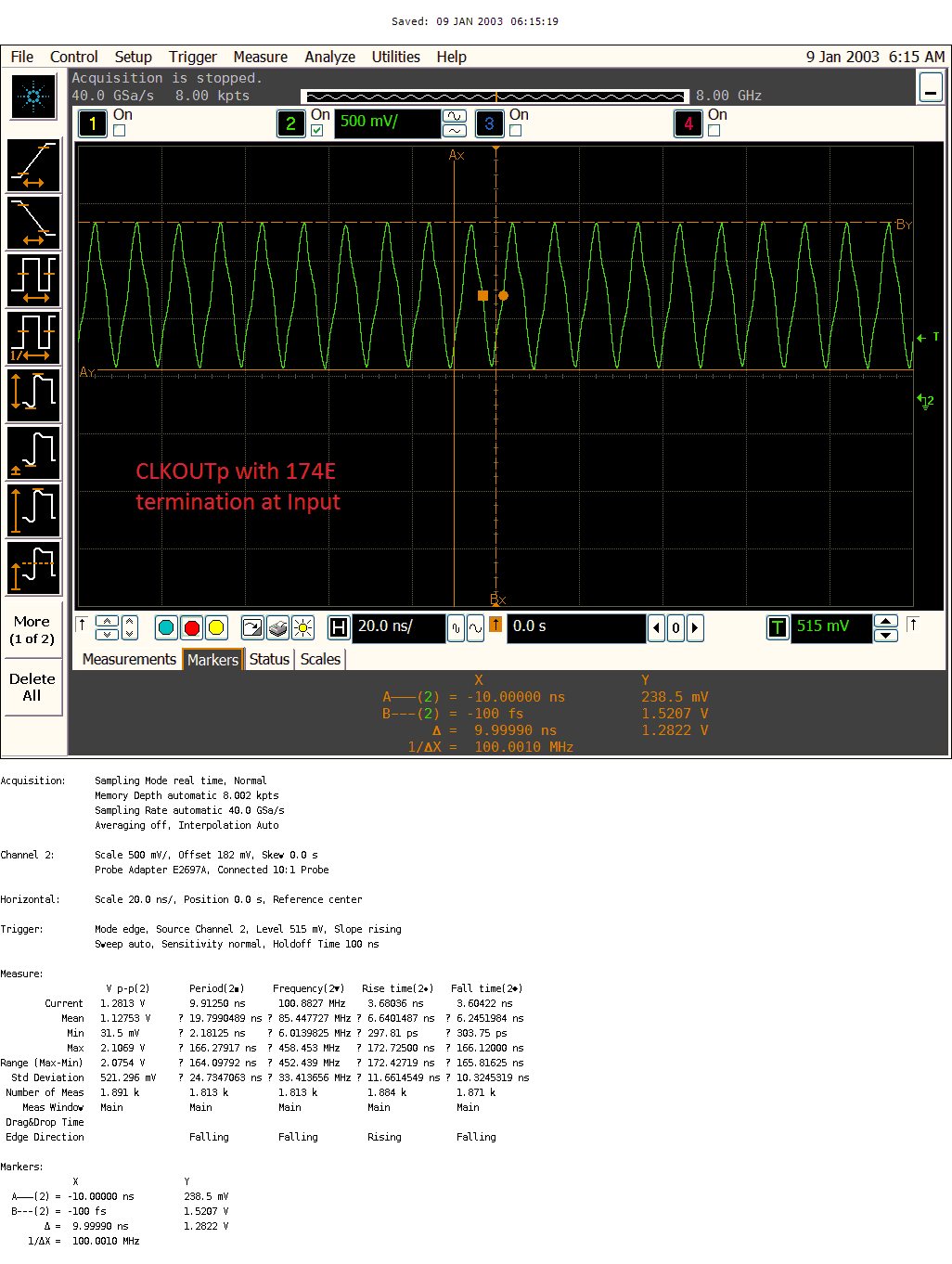

板1) ADC ADS4245-EP CLKOUT p/n 振幅未达到预期水平 -接近500mVpp (其中、与工作卡中的一样、接近1Vpp)

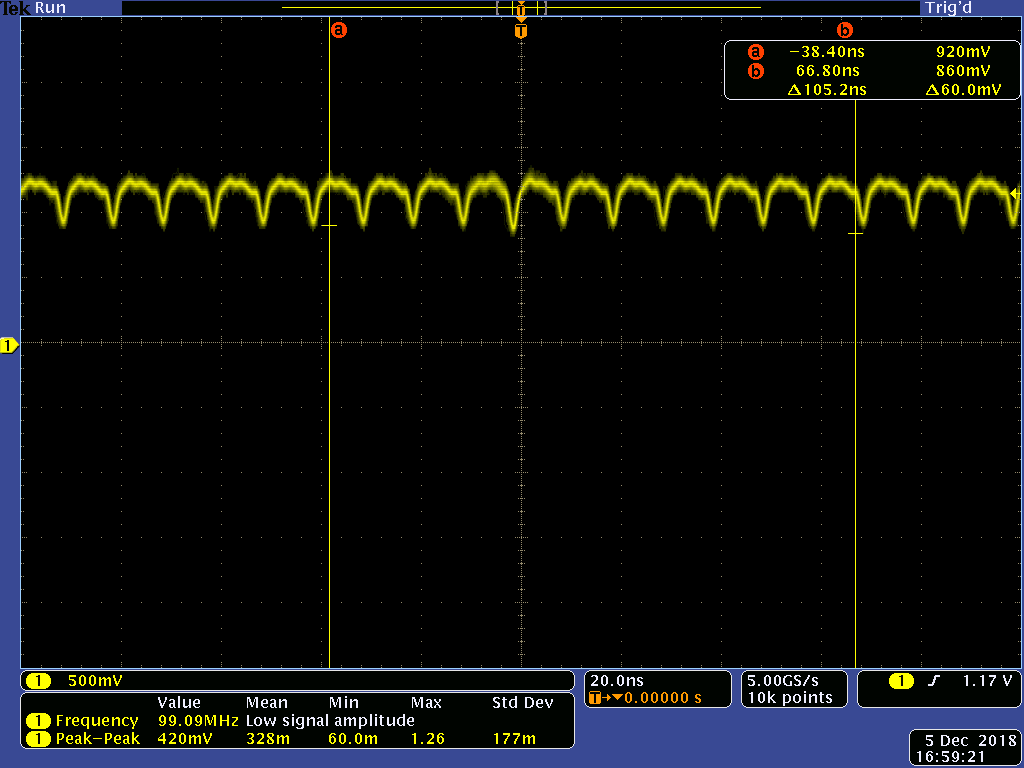

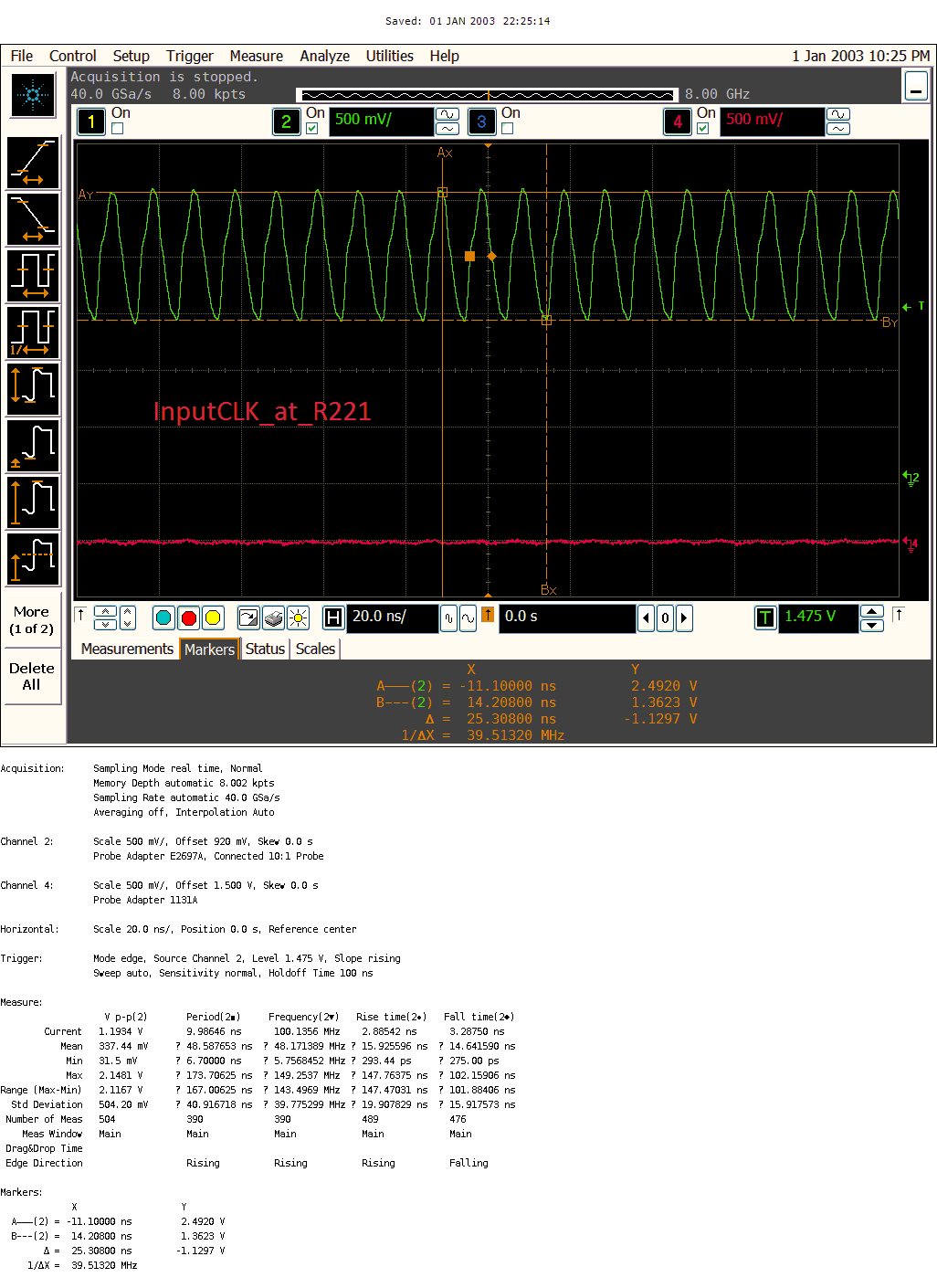

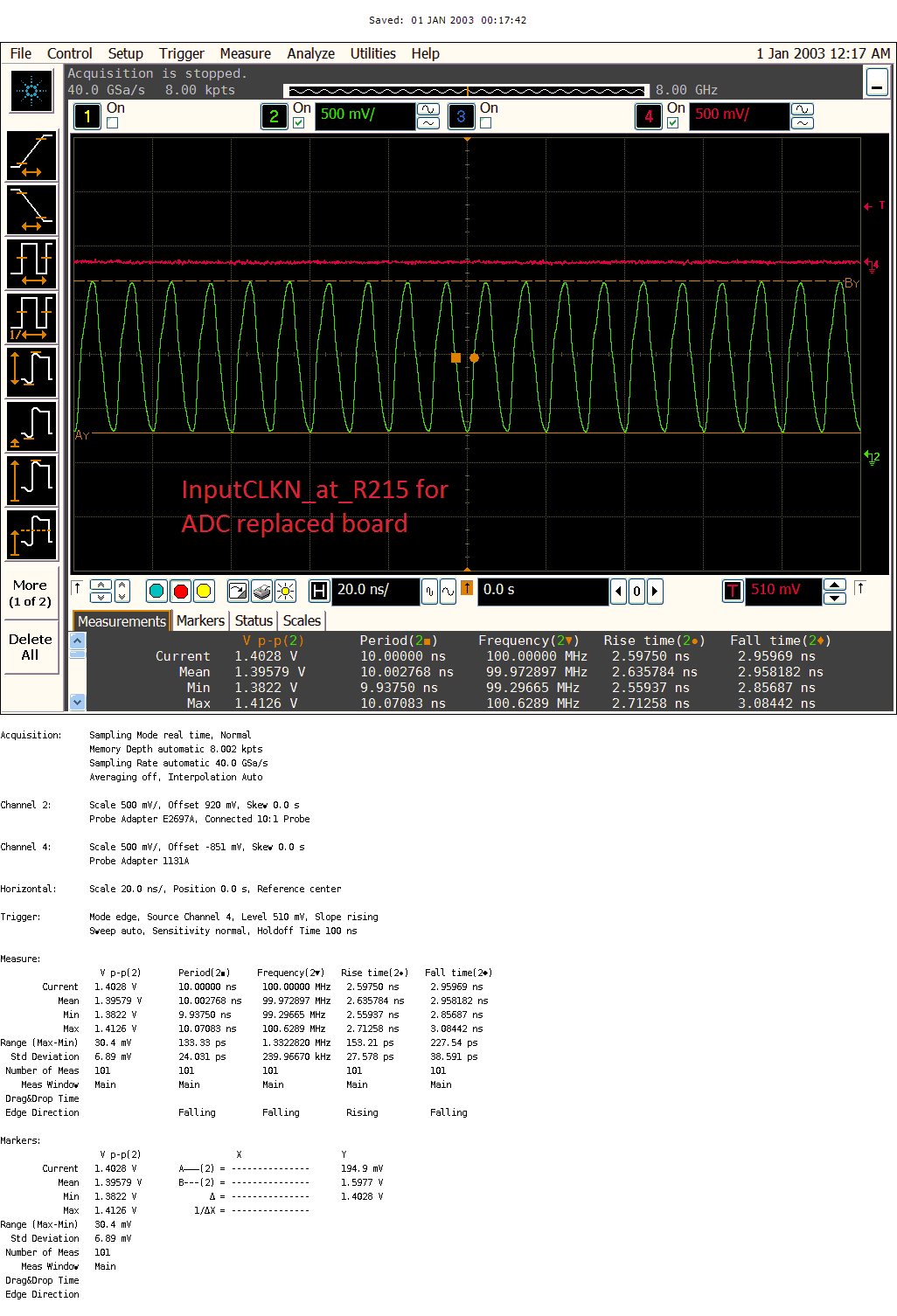

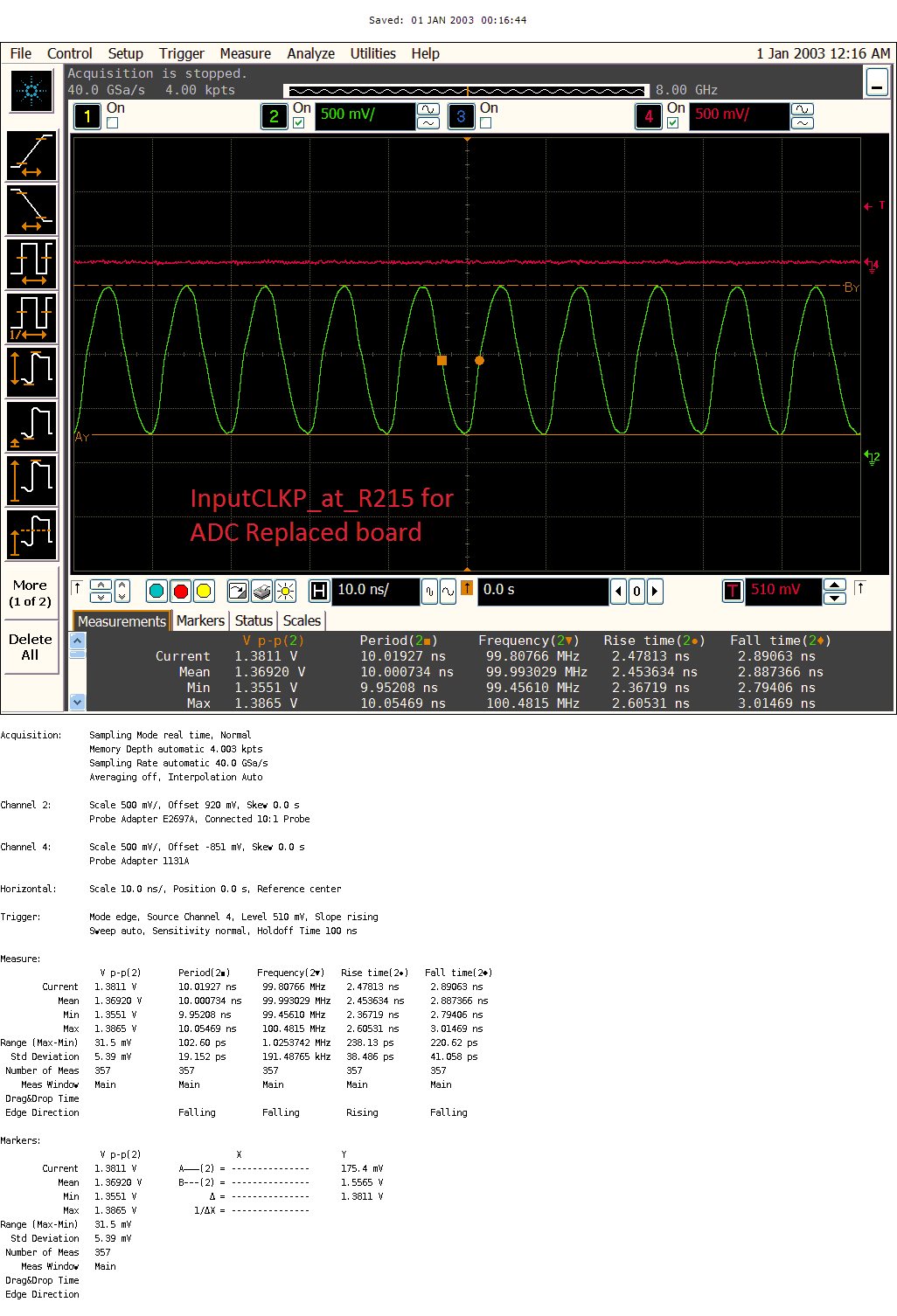

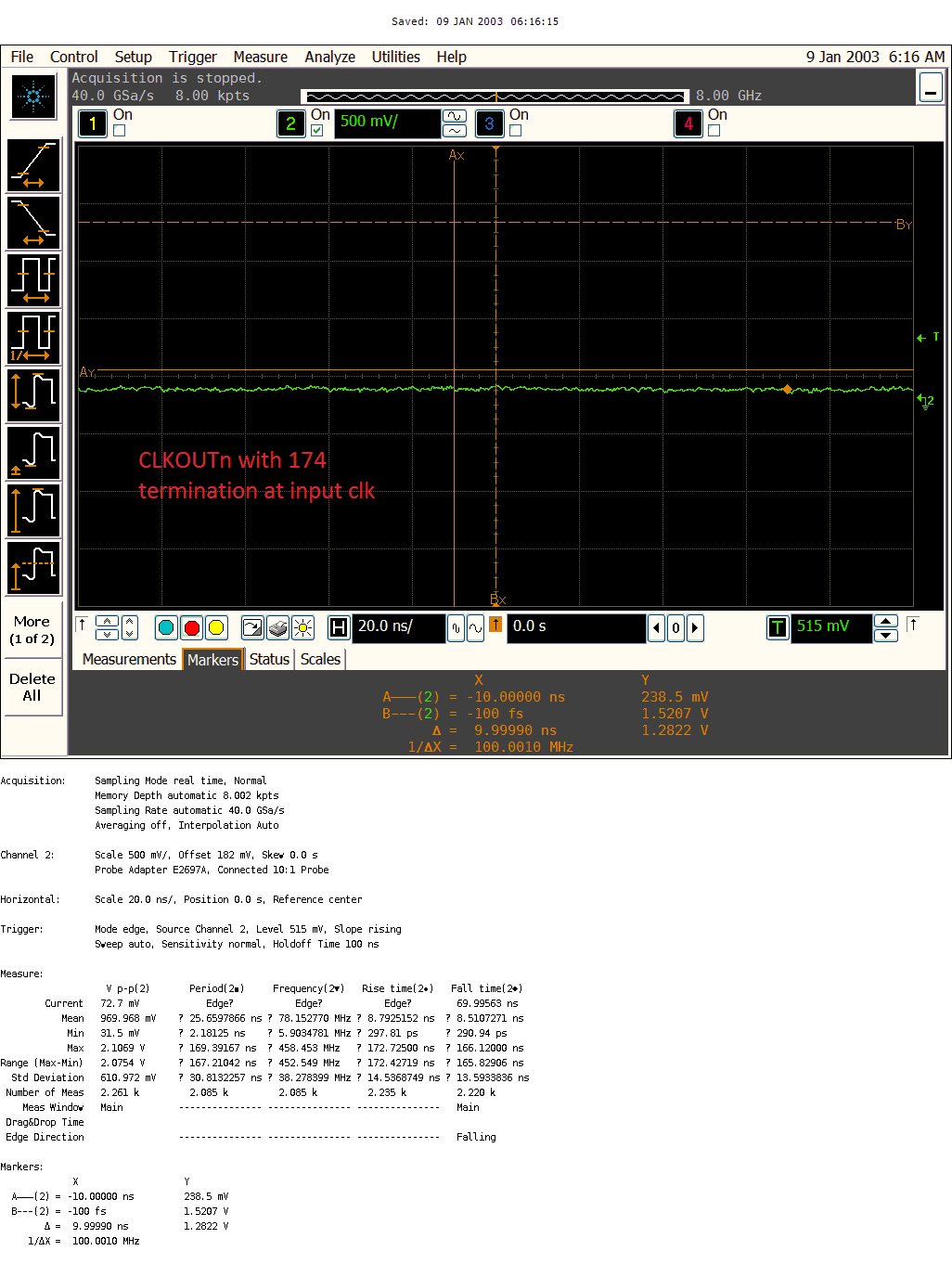

2) ADC ADS4245-EP CLKOUT_p 存在 -几乎为1Vpp、而 CLKOUT_n 不存在。 (器件引脚和监控点之间通过导通)

我怀疑 ADC 是否出现故障。

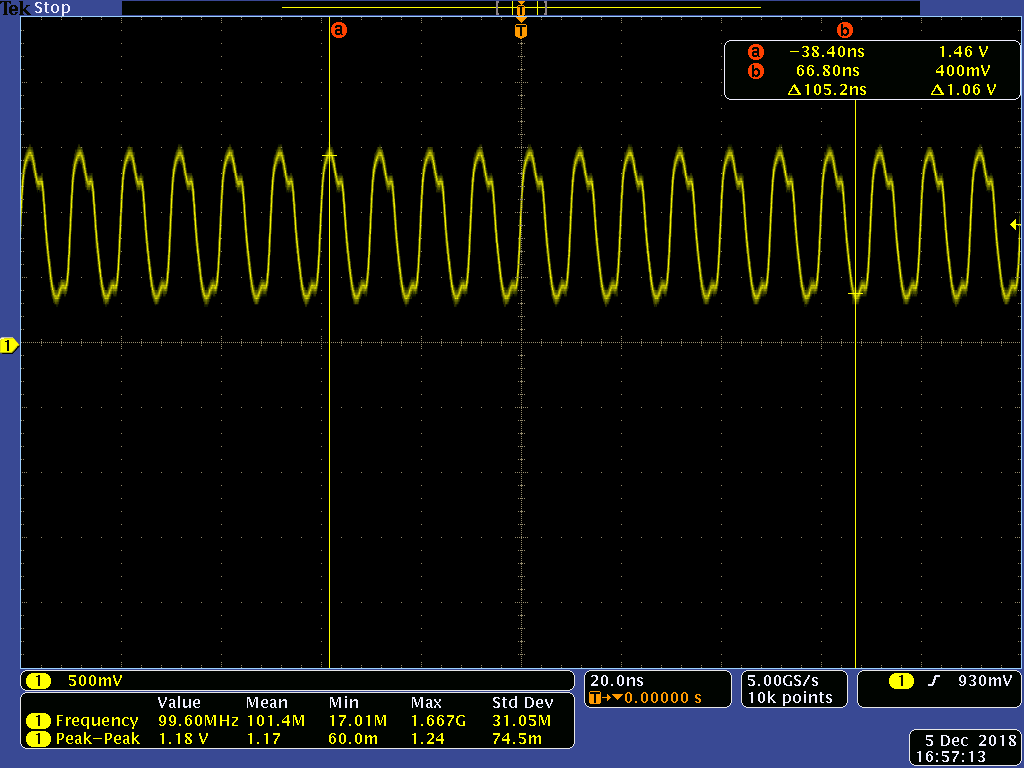

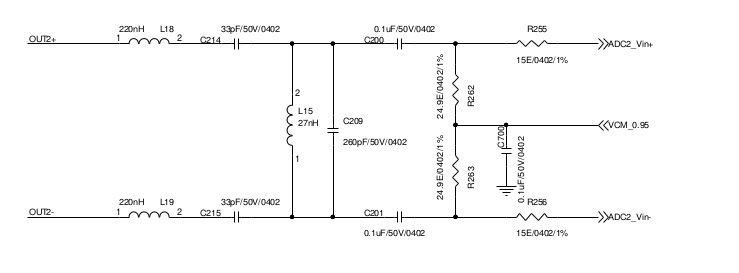

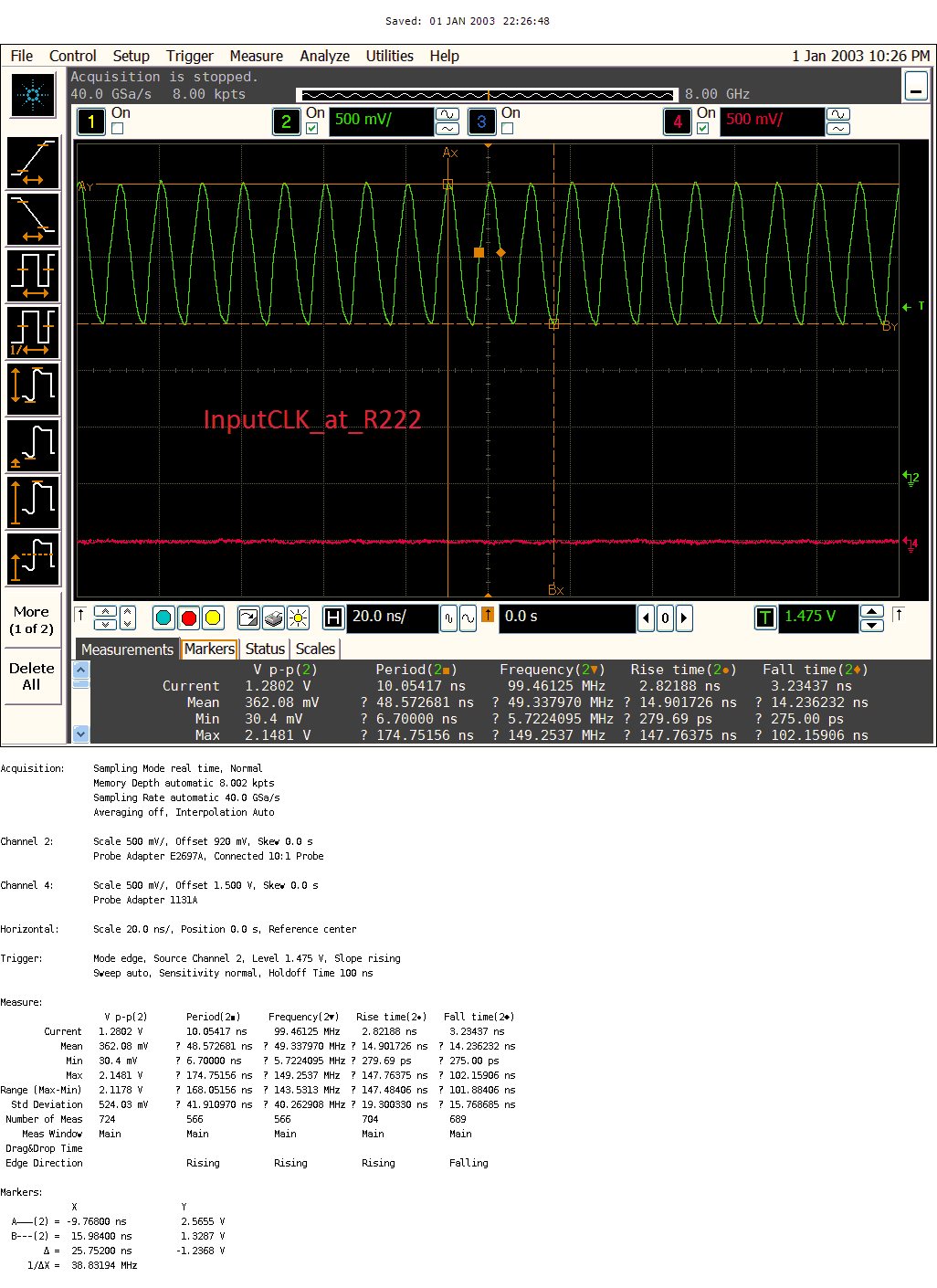

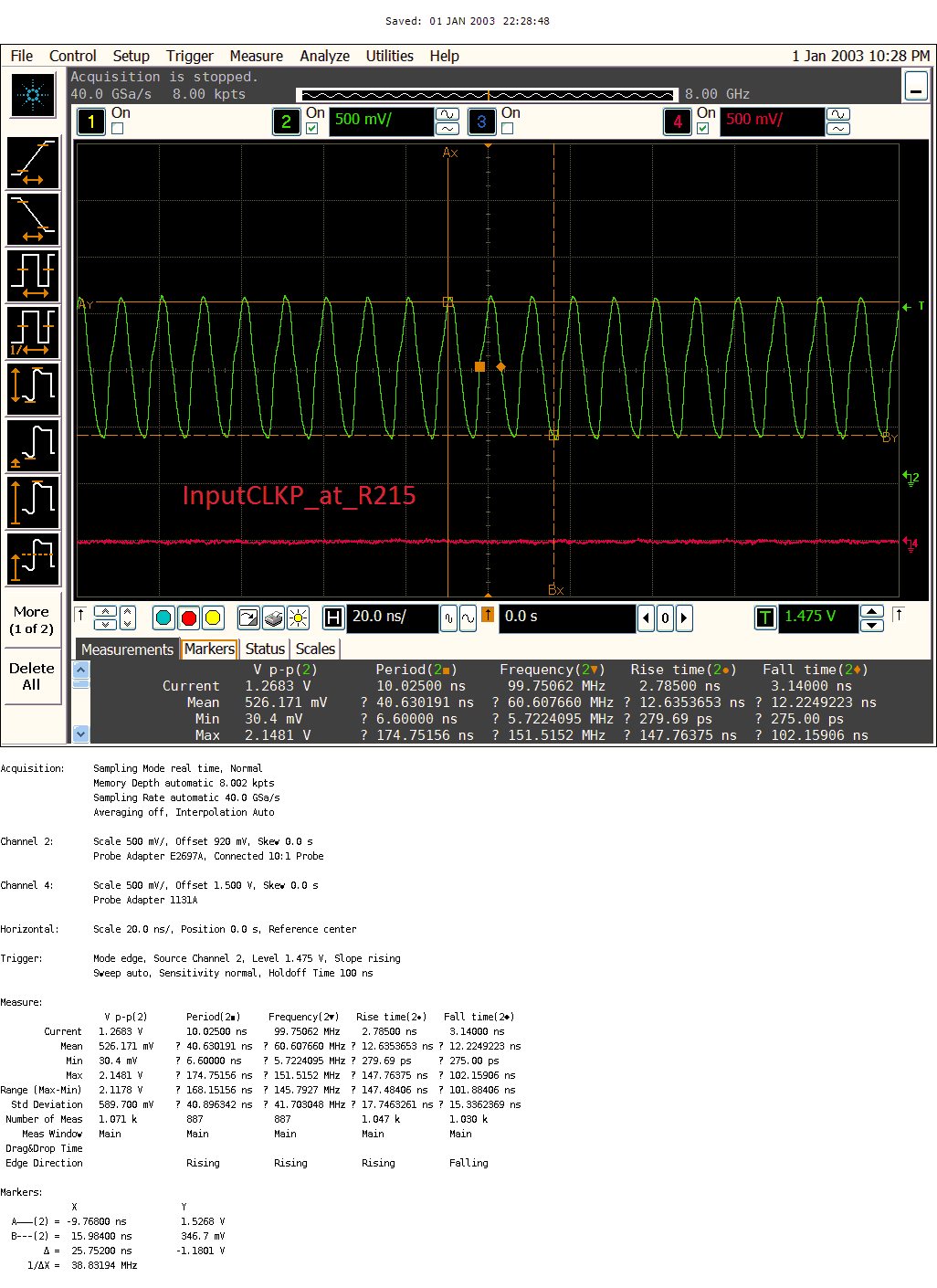

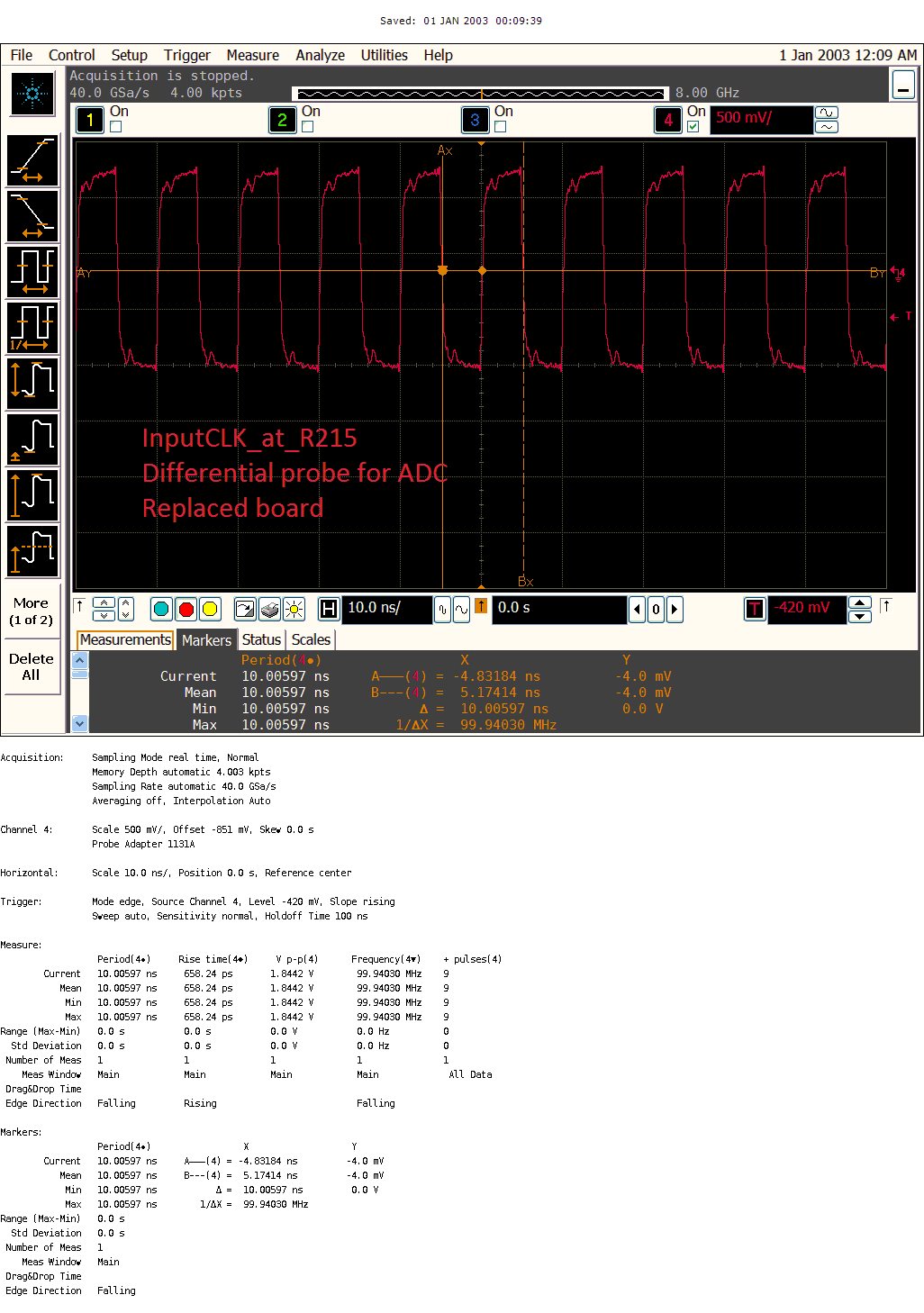

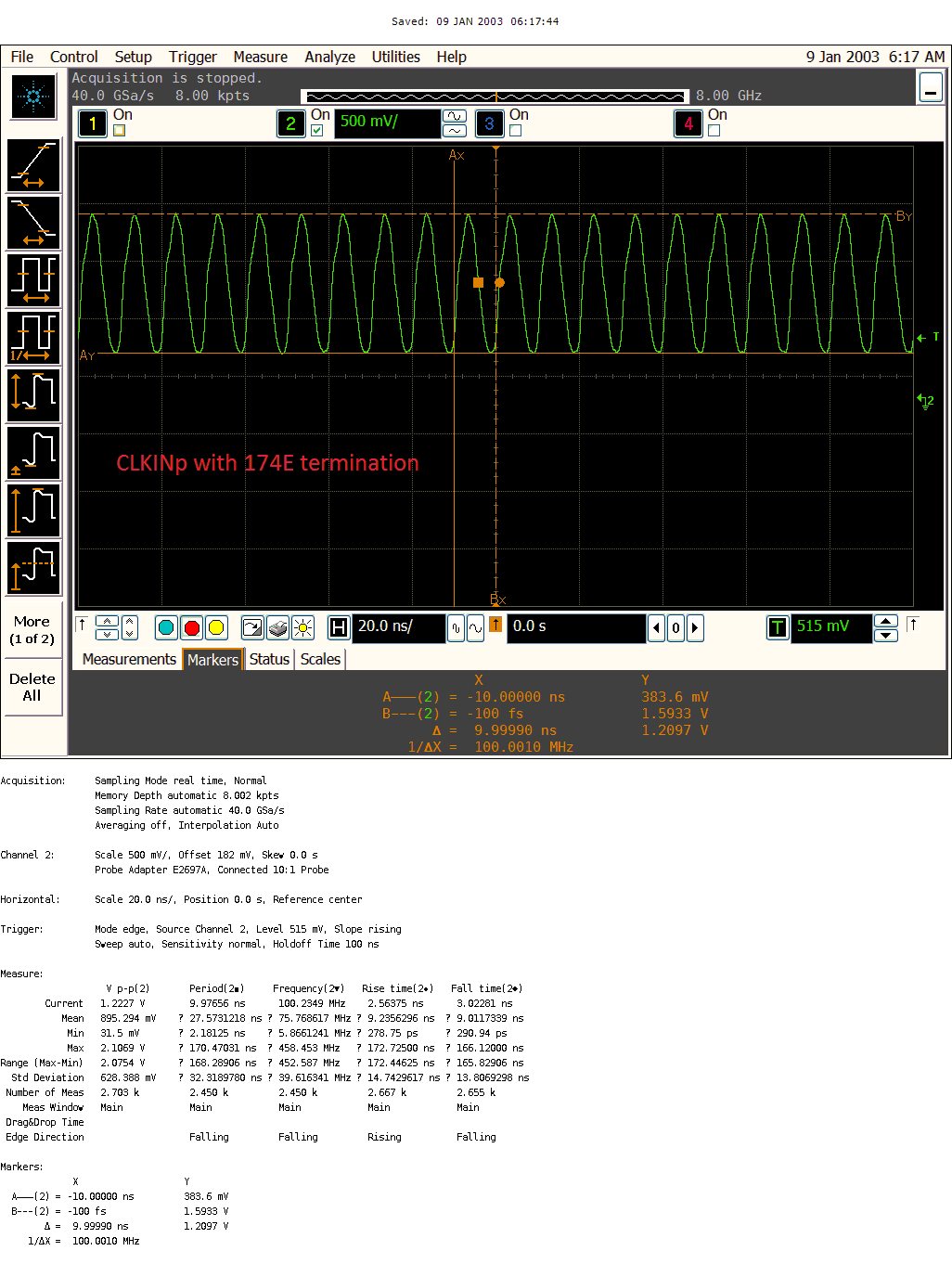

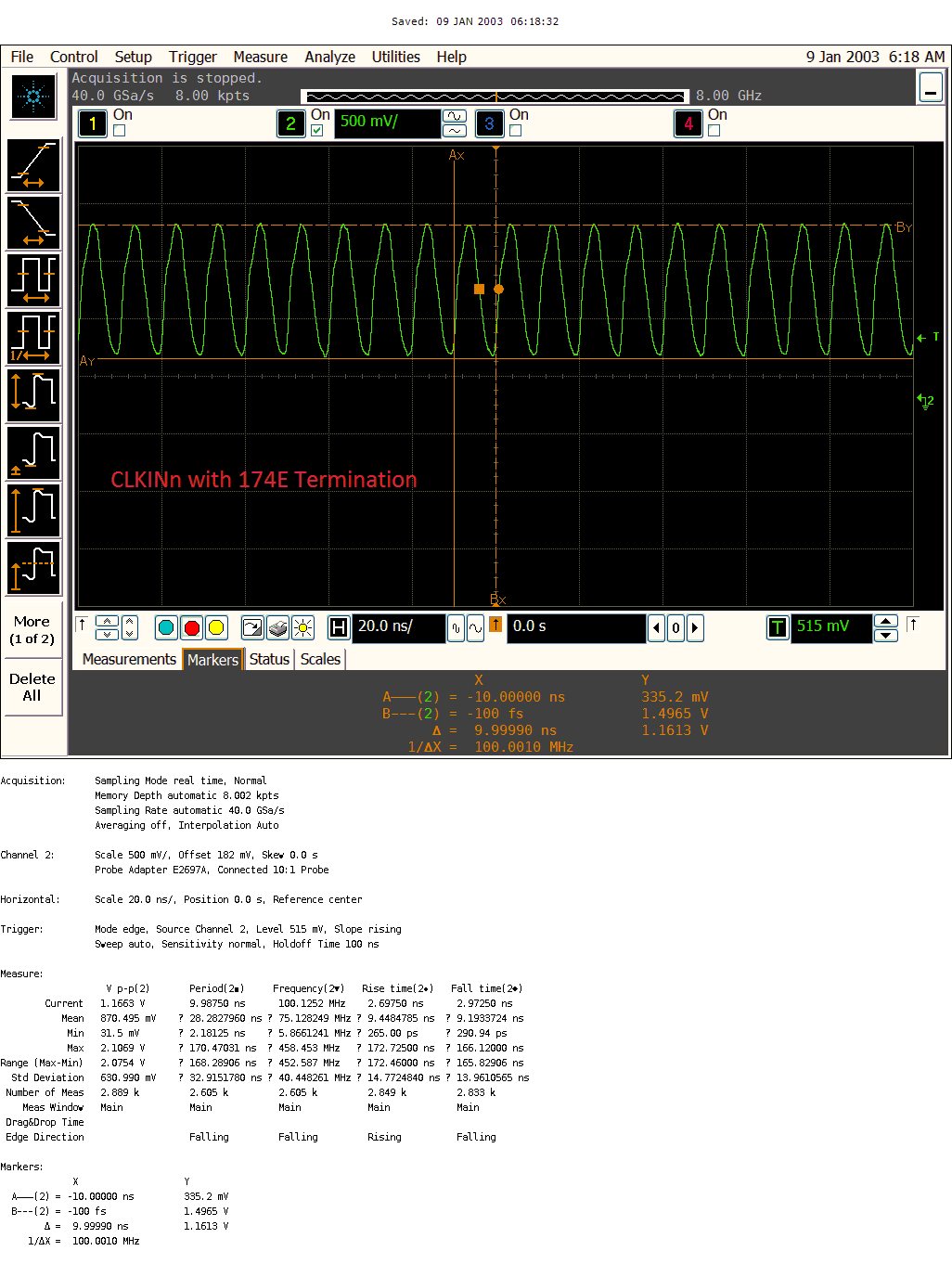

所有3个电路板具有相同的时钟输入。 (探测和验证)

请发表评论。