主题中讨论的其他器件:ADS54J60、 LMK04828、 ADS54J69

我们目前正在为一个项目评估 ADS54J60、并且需要能够相对于 FPGA 移动 ADC 的采样阶段(有多个 ADC、每个 ADC 具有单独的采样延迟)。

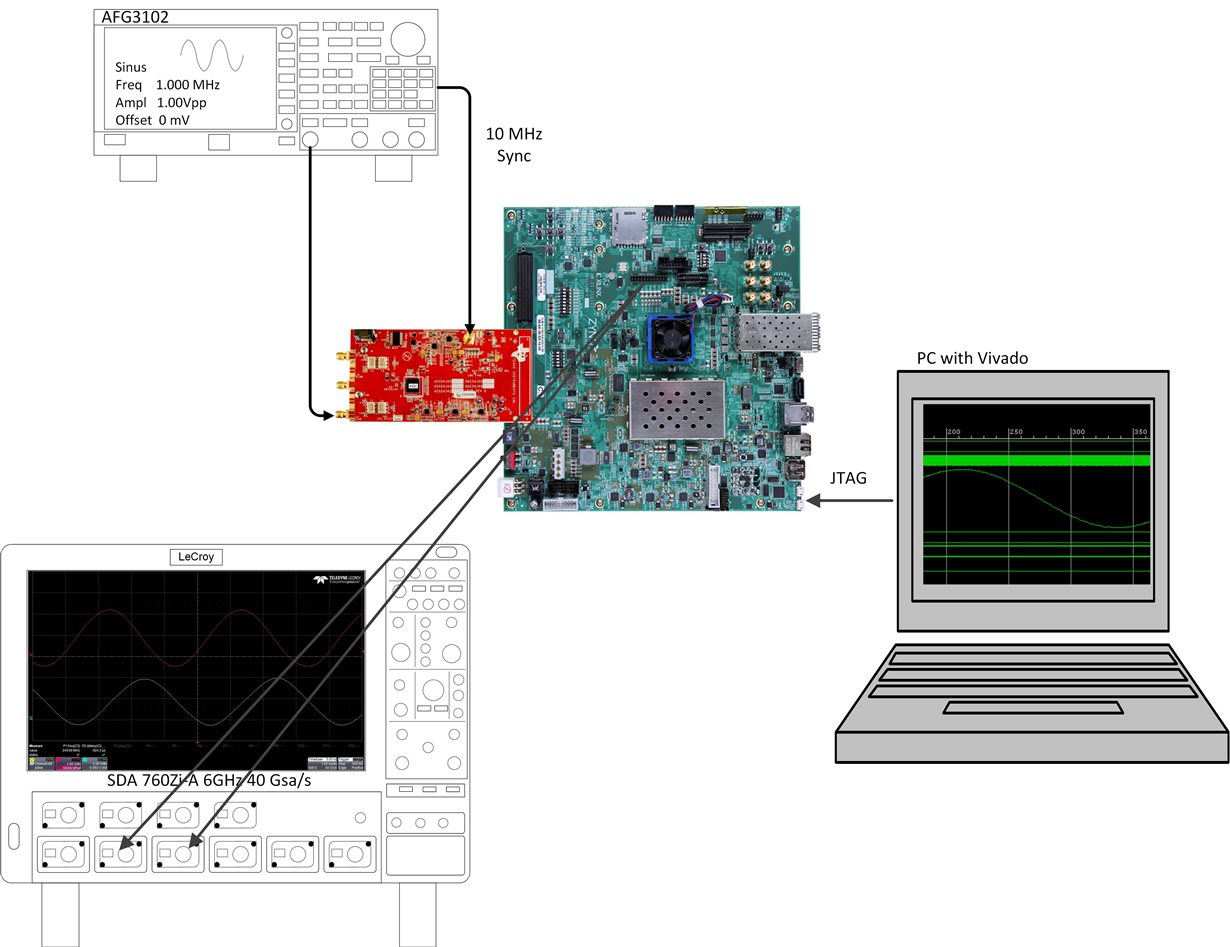

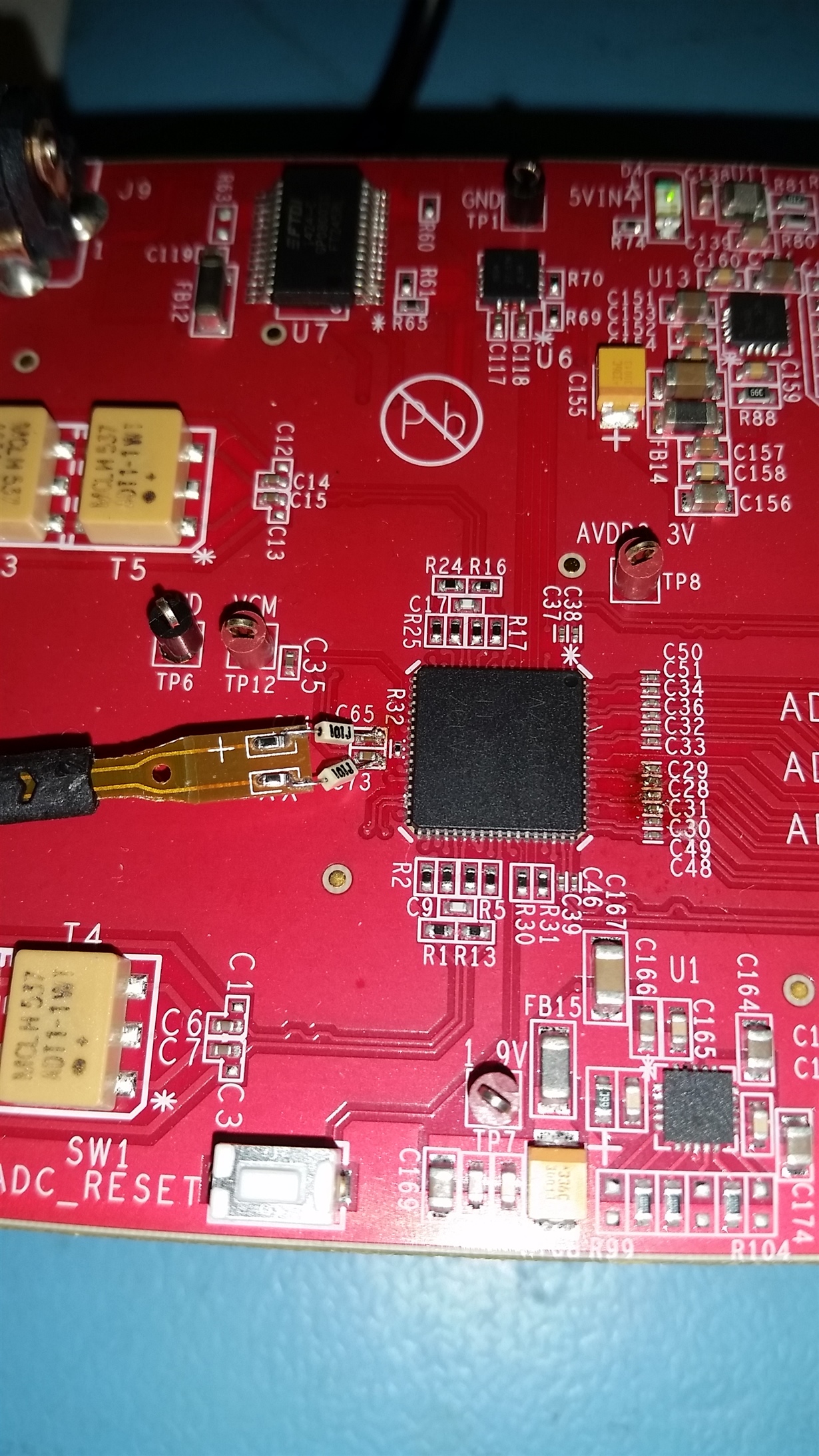

ADC 数据以500 msA/s @ 16位= 8 Gbit/s =>使用 JESD204B 的8B/10B 进行采样、最终结果为10 GSA/s、并路由到 FMC 连接器上连接到 Zynq Ultrascale+ MPSoC FPGA 的 Xilinx ZCU102板。

我看到系统工作正常、并使用 Xilinx 的集成逻辑分析仪(ILA)检查 ADC 中的数据、并查看干净和正确的数据。

现在、我开始在评估板上移动时钟分配芯片 LMK04828、输出 DCLK 2、模拟延迟、步长为25ps。 我能够使用示波器观察参考时钟和 FPGA 恢复时钟之间的相移... 因此 、该部件正常工作。

在大约950ps 的模拟延迟下、FPGA 无法再锁定 ADC 数据并提供大量垃圾。 甚至 K28.5也不再被正确采样。

现在、我的问题_是否有人尝试使用 JESD204B 接口成功移动 ADC 的采样阶段? 从理论上讲、这应该是可行的、因为 FPGA MGT 的运行频率略有不同、因此我本来希望使用 JESD204B 也是可行的... 特别是因为我只发送用于对齐符号的 K25.5字符。

谢谢

Goran