您好、支持人员、

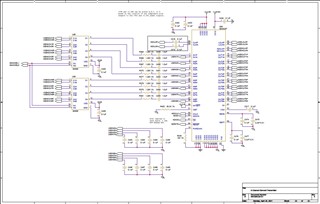

我们正在尝试将测试斜坡波形接收到我们的 FPGA 中、而无需任何下降数据。 我连接了差分时钟输入信号。 输入时钟信号具有电容器耦合、如原理图所示。 中的时钟速率为16MHz、我们将 FPGA 中的采样速率降至4MHz。

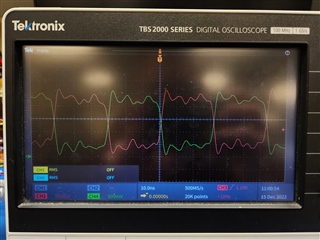

原始斜坡数据转储到 Excel 电子表格中、并按屏幕截图所示绘制。 您可以看到、大多数数据都很好、但我们有一些地方会出现数据干扰。 我还附上了 LCLK 和 ACLK 的屏幕截图、其中似乎存在一些抖动。

该器件上有一些寄存器可以调节 PLL、但规格中的描述并未非常详细地说明如何使用它们。 正在寻找解决我们的故障(硬件模块? 还是写入 PLL 寄存器??) 请帮助。

此致、

Mike

e2e.ti.com/.../ADS5287_5F00_Ramp_5F00_Output_5F00_Data.pdfe2e.ti.com/.../ADS5287_5F00_Ramp_5F00_Output_5F00_Slower_5F00_Decimation.pdf