Thread 中讨论的其他器件: 、Strike、 ADS54J20

在以下设置中、我们看到 FPGA 上接收到的 ADC 数据中的 A0 (1:0)和 B0 (1:0)位置有一些卡住的位。

有时位0在数据中切换、有时会卡住。 但位1始终卡住。

如果我们"触发 ADC 数据"、则卡滞位的位置更改为 A0 (14:15)和 B0 (14:15)

如果我们使用12个八位位组 RPAT JESD 测试模式、则没有卡住的位。

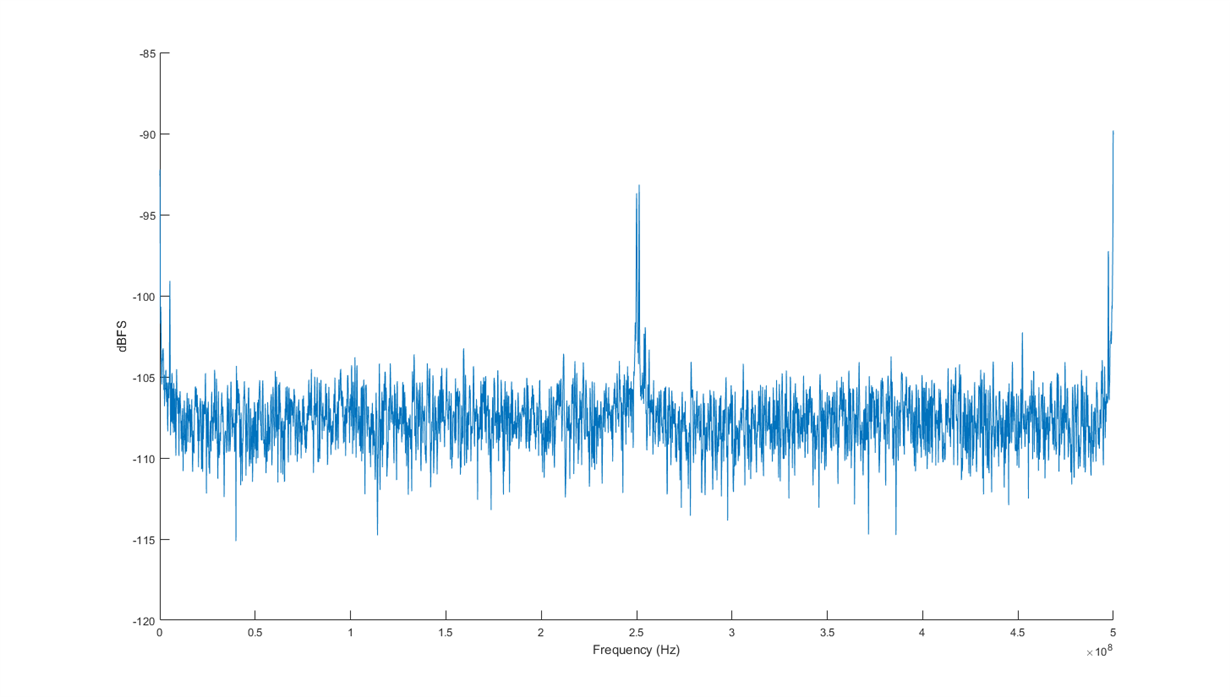

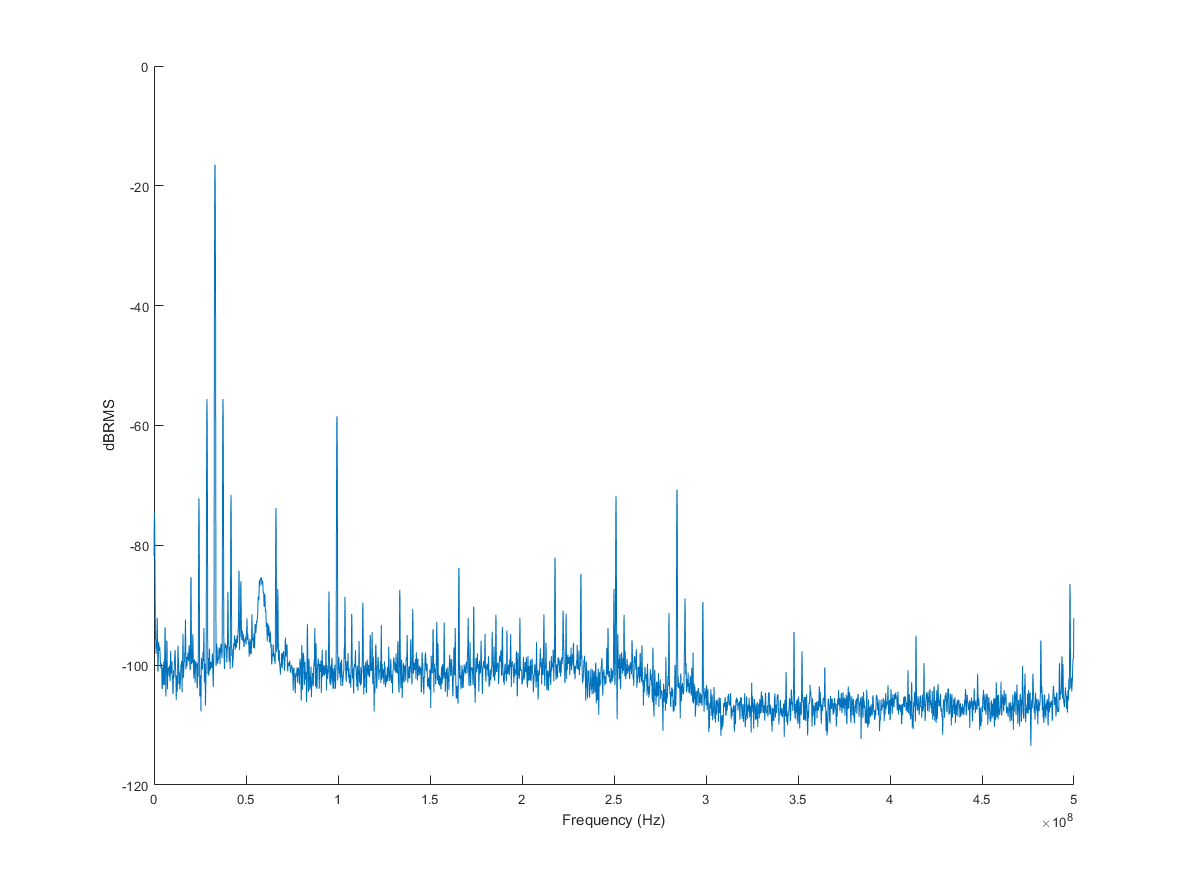

(下图显示了从3种场景中捕获的内容)

我们根据以下设置在定制板中观察到同样的情况。

设置:

ADS54J60EVM 连接到 Xilnx KCU105

使用外部1GHz 时钟

FPGA 时钟= 250MHz

K = 16

SYSREF 分频器设置为256

SYSREF 处于连续模式

我们遵循的步骤如下:

对 FPGA 进行编程

加载修改版本的 LMK_Config_External_Clock 以生成所需的时钟和参考频率

按下 ADCReset 按钮

加载 ADS54J60_LMF_8224.cfg

我已经尝试过此文件的修改版本来删除 LMK 写入以使 sysref 生效和失效(正如我们希望的连续版本)、但这没有什么区别。

您能建议我们的设置中出现任何会导致此问题的问题吗?

此致