主题中讨论的其他器件: DAC34SH84

你好

我正在使用 dac34h84 EVM,我有一些问题吗?

1.是否可以将 DAC 配置为 FIFO 禁用模式? 如果是,那么读取频率是多少,读取频率取决于什么?

2.在 fifo 禁用模式下,我是否可以为 DATA_clk 和 DAC_clk 提供相同的频率?

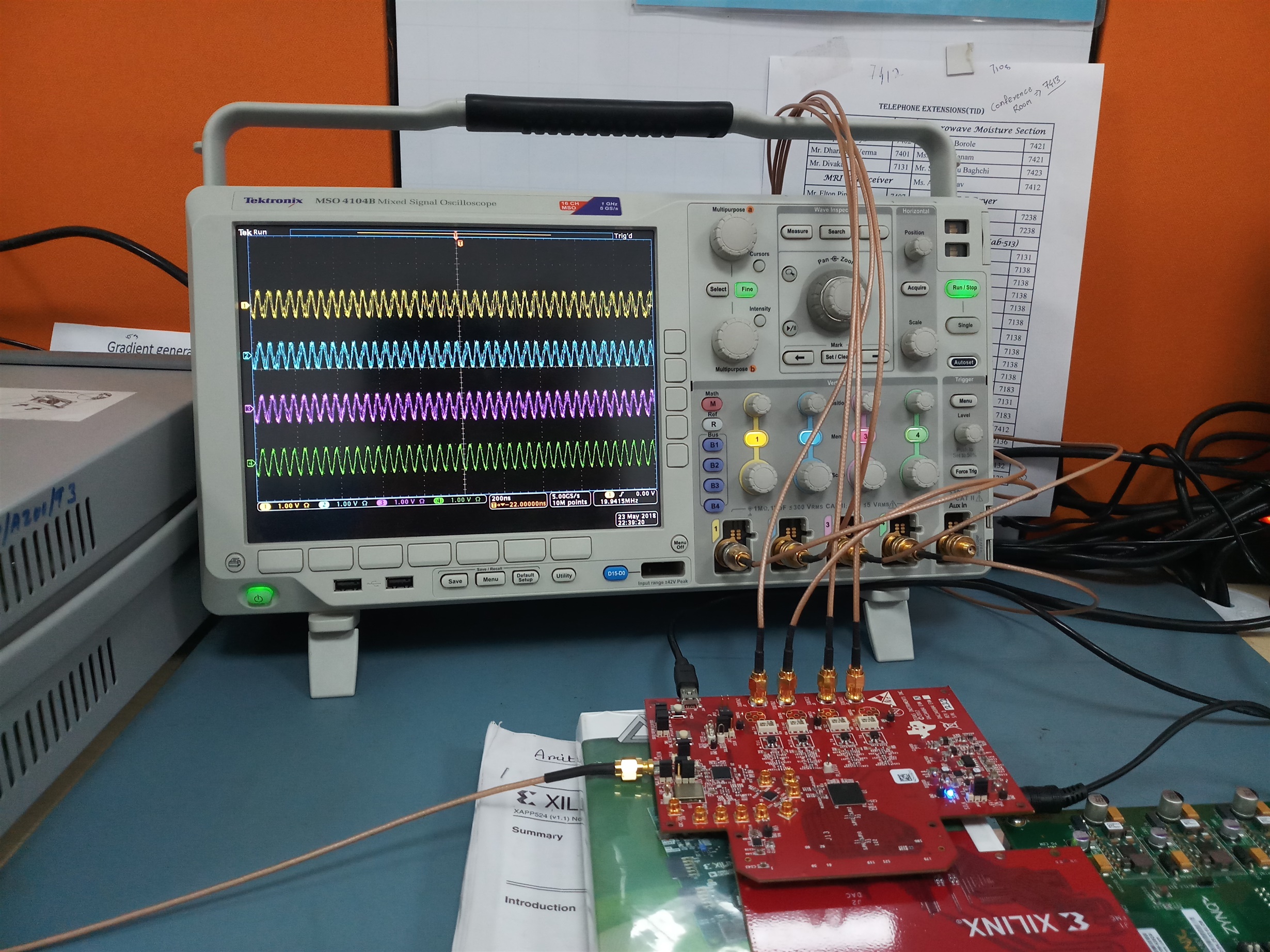

3.在 dac34h84 EVM 上,“SH3”提供了 dacclk2,因为我有 FMC DAC 适配器,我可以向 FPGA 提供该时钟,还是从 FPGA 获取它? 如下图所示

4.如果我生成的波形与 dac34h84第26页的数据表中所示的波形相同,那么我需要注意哪些额外的信号,例如 OSTR,因为我不使用 FIFO?