请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS1234 您好!

我们使用 ADS1234进行了设计、以测量四个负载单元。

当引脚 DRDY/DOUT 变为低电平时、我将使用 MCU 的 SPI 读取数据。

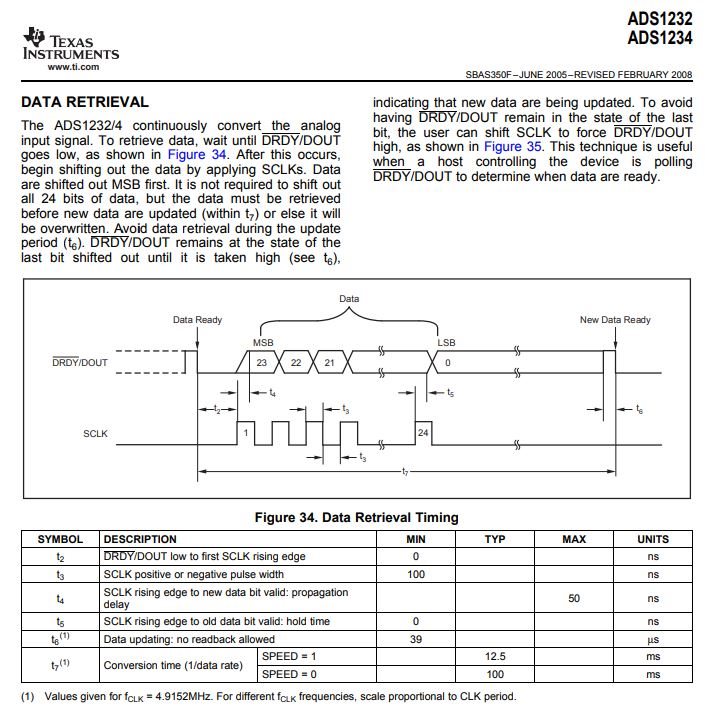

根据数据表、在部分数据 RETRIEVEL 上、我们设置的 SPI 速度足够快、可以获得50ns 的负时钟或正时钟。

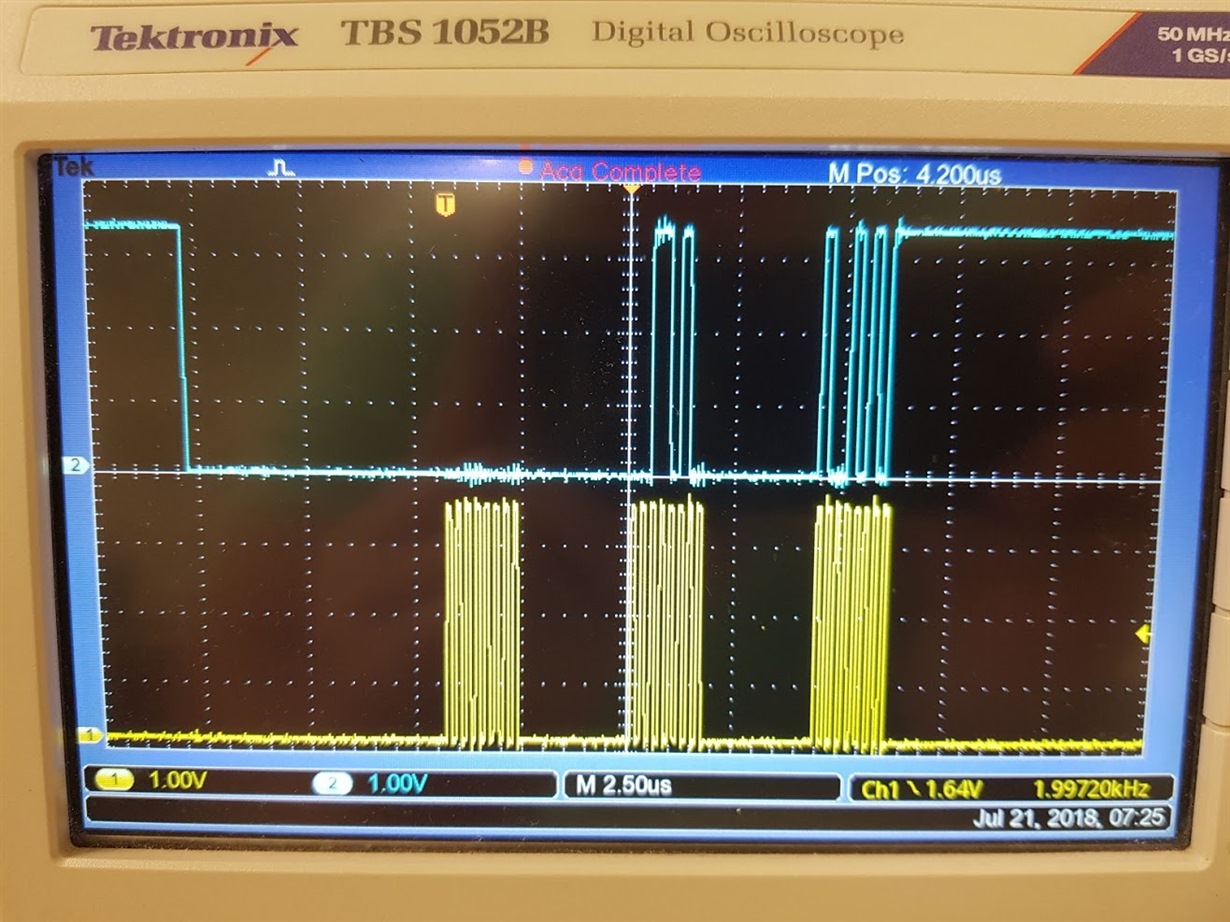

使用示波器、我们可以看到时钟信号的50ns、但当我读取数据时、时钟信号不是恒定的。 下图显示了我的 MCU 的行为。

SPI 的这种行为可能会给 ADS1234带来问题?

时钟信号需要保持恒定? 每个时钟的间隔为2.70us。

为了读取所有24位、在 DRDY/DOUT 变为低电平后、SPI 花费@ 16.25us 的计数。

根据数据表、DRDY/DOUT 信号变为低电平后、我有100ms 的时间来读取所有24位。

我的速度设置为10SPS。

我想仔细检查时钟信号的这种行为、并确保这不会对我们造成问题。

谢谢!!