主题中讨论的其他器件: DAC3484、 DAC38J84

大家好、

我的客户在信号发生器板中使用 DAC3482。 对于某些特定的电路板、我们发现了一个奇怪的现象。 首先、DAC3482工作良好。 在它运行几分钟后、我们将电路板断电并再次为其加电、我们发现 DAC3482输出丢失。 输入时钟和 FPGA 输入数据均已存在。 当我们手动冷却器件并重新启动时、DAC3482输出会再次显示。 此问题在10个板中的3个板上发生。

输入时钟为500MHz。 内插= 2。 数据速率=500Msps。 fdac=1GSPS

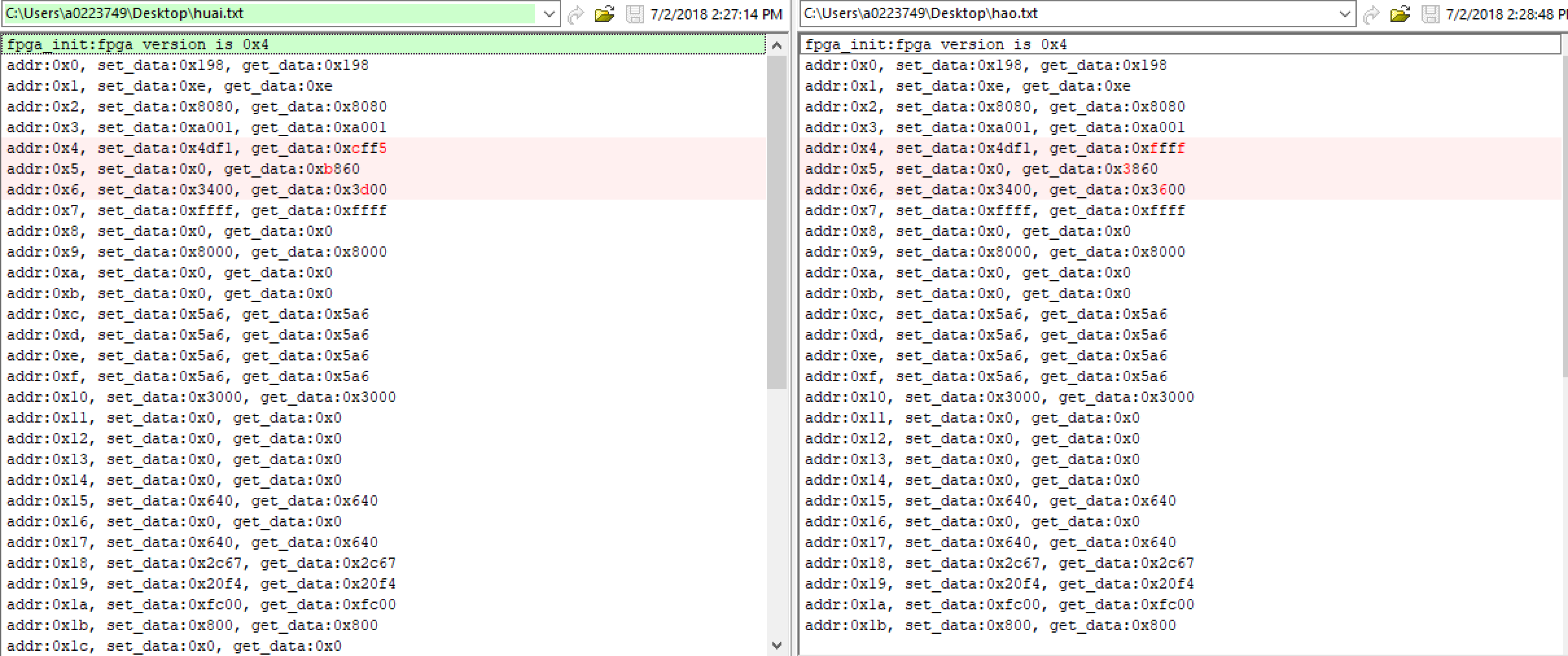

我们读取寄存器值、如下所示。 当没有输出时、读取左列。 当有输出时、读取右侧列。

对于寄存器0x4,该值不同,但客户没有在 reg1中启用“iotest_ENA”。 那么、为什么该值不同呢? 这是否与输出丢失问题有关?

对于寄存器0x5,即使在右列(DAC 工作正常)中,位13-11都是1,这意味着“FIFO 指针冲突警报”。 当 DAC3482工作良好时、您认为发生此警报是否正常?

此外,在左列中,位15是1,与右列不同。 这意味着 alarm_from _zerochk。 您认为这与输出丢失问题有关吗? 如果是、我们如何消除该警报?

对于寄存器0x6、这意味着读取的温度值。 我们在冷却器件后读出正确的列值。 因此、右侧的值小于左侧的值、这是合理的。 但是、即使在输出丢失时、温度也不是那么高。

希望您能帮助找出导致输出丢失问题的根本原因。 如果您需要更多测试结果、请告诉我。 谢谢。

此致、

韦恩