您好!

我有 DAC7678EVM、并将其配置为如下所述。 我能够以接近400kHz 的频率成功地与器件通信。

我在向任何通道输出模拟电压之前尝试配置器件、我发现 LDAC 和内部基准寄存器干扰掉电寄存器。

--------------------

序列:

- 写入序列到软件复位: 0x70、M 0x00、L 0x00

- 循环和读取寄存器:

PWRDOWN_REG: 0x0000

CLEARCODE_REG: 0x0000

LDAC_REG: 0x0000

INTREF_STATUS_REG:0x0000

INTREF_FLEX_REG: 0x0000

- 写入序列以清除代码寄存器: 0x50、M 0x00、L 0x30

- 清除代码寄存器的读取序列: M 0x00、L 0x03

- 将序列写入 LDAC 寄存器: 0x60、M 0xFF、L 0x00

- LDAC 寄存器的读取序列: M 0x00、L 0xFF

- 循环和读取寄存器:

PWRDOWN_REG: 0x00F8 <--为什么? 预期: M 0x0000

CLEARCODE_REG: 0x0003

LDAC_REG: 0x00FF

INTREF_STATUS_REG:0x0000

INTREF_FLEX_REG: 0x0000

- 将序列写入掉电寄存器: 0x40、M 0x5F、L 0xE0

- 清除代码寄存器的读取序列: M 0x02、L 0xFF

- 循环和读取寄存器:

PWRDOWN_REG: 0x02FF <--正常

CLEARCODE_REG: 0x0003

LDAC_REG: 0x00FF

INTREF_STATUS_REG:0x0000

INTREF_FLEX_REG: 0x0000

- 将序列写入内部参考静态寄存器: 0x80、M 0x00、L 0x00

- 内部参考静态寄存器的读取序列: M 0x00、L 0x00

- 将序列写入内部参考灵活寄存器: 0x90、M 0x50、L 0x00

- 内部参考静态寄存器的读取序列: M 0xA0、L 0x00 <--为什么? 预期: M 0x00、 L 0x05

- 循环和读取寄存器:

PWRDOWN_REG: 0x0280 <--为什么? 为什么这种情况再次发生变化?

CLEARCODE_REG: 0x0003

LDAC_REG: 0x00FF

INTREF_STATUS_REG:0x0000

INTREF_FLEX_REG: 0xA000 <--为什么? 这毫无意义。

--------------------

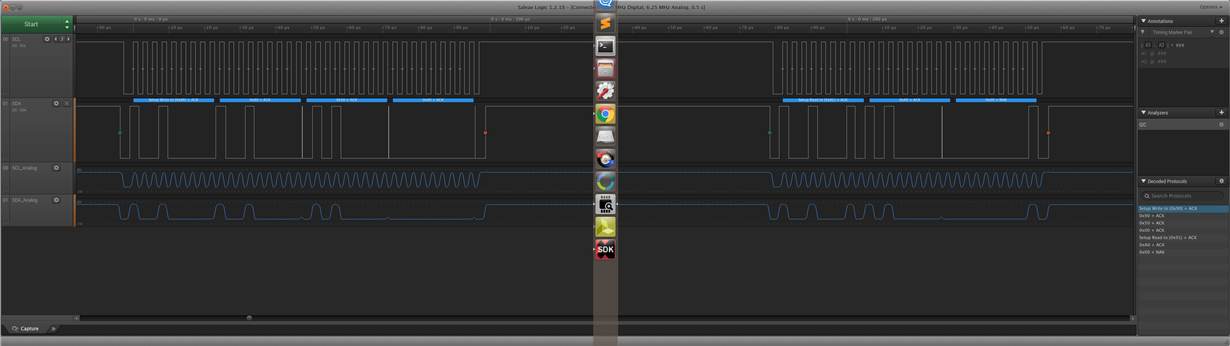

我很难理解为什么当我写入 LDAC 或内部基准寄存器时断电寄存器会改变值。 使用逻辑分析仪/示波器时、I2C 信号看起来良好。

我正在使用以下 配置...

JP1、JP2和 JP10开路

JP11关闭

JP4闭合1/2位置

JP6闭合1/2位置

JP7闭合1/2位置

JP3悬空

JP8和 JP9闭合2/3位置

J3.3处为+5V

J3.5和 J2.10上的 GND

SCL 位于 J2.16

SDA 位于 J2.20

感谢您提前提供的任何帮助!

Phil