Other Parts Discussed in Thread: ADS131E08

大家好、

我设计了一个采用 ADS131e08 ADC 和 Spartan6 FPGA 的数据采集系统。

我配置 ADC 并通过 VHDL 代码读取其中包含多种状态的数据。 在此状态下、ADC 首先复位、然后 Config 寄存器设置正确。

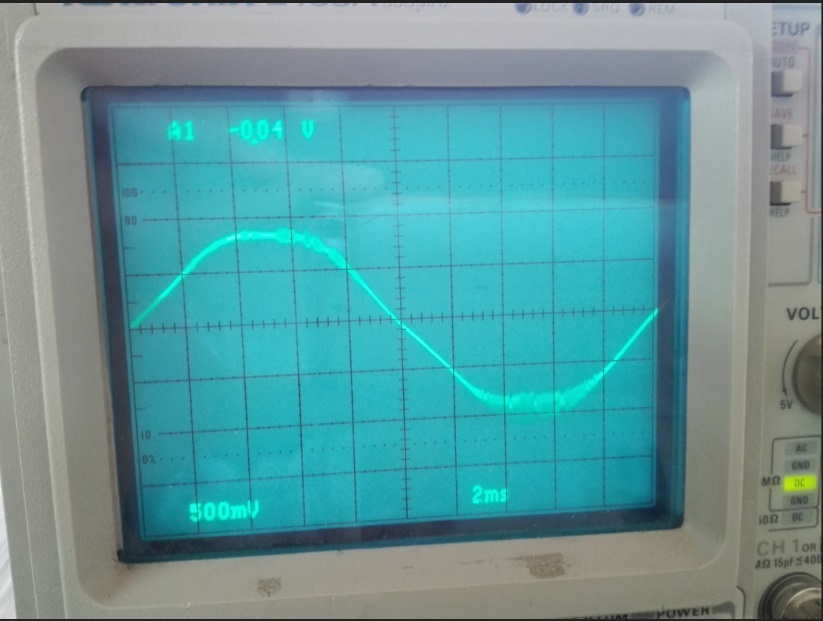

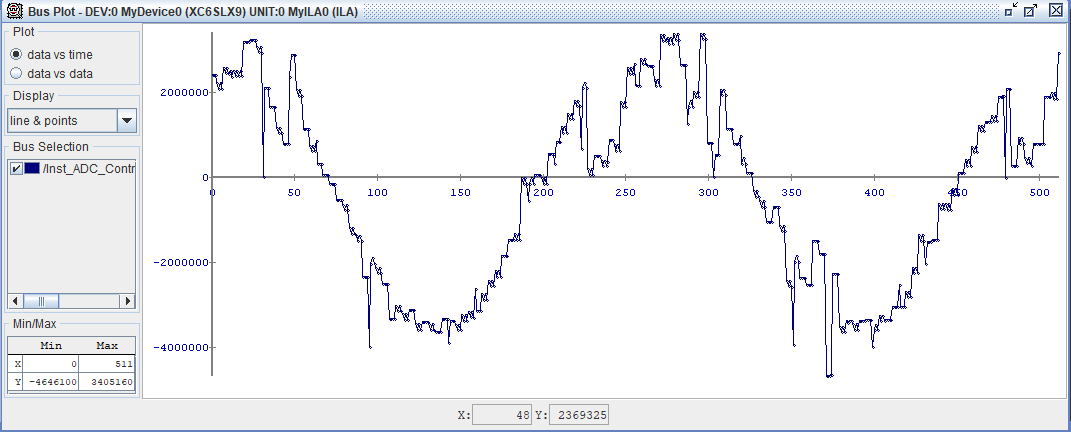

我使用 Xilinx Chipscope 捕获接收到的数据。 当 ADC 的模拟输入设置为直流值时、芯片范围内接收到的数据是正确的、没有问题、但是当模拟输入连接到交流值(正弦波)时、接收到的数据不是正弦波。

我将 ADC 参数设置为:

Fclk= 2.048MHz

Fsclk = 18.432MHz

Fchipscope=2* Fsclk

数据传输速率:1KSPS

分辨率= 24位

AVDD =+2.5V

AVSS =-2.5V

小于 ADC Vp-p = AVDD - AVSS 的正弦波(PEEK 至 PEEK = 4V)。

我想问题与 Chipscope 设置相关?权限?

请帮助我解决此问题。

此致、