Other Parts Discussed in Thread: AFE5809

你(们)好

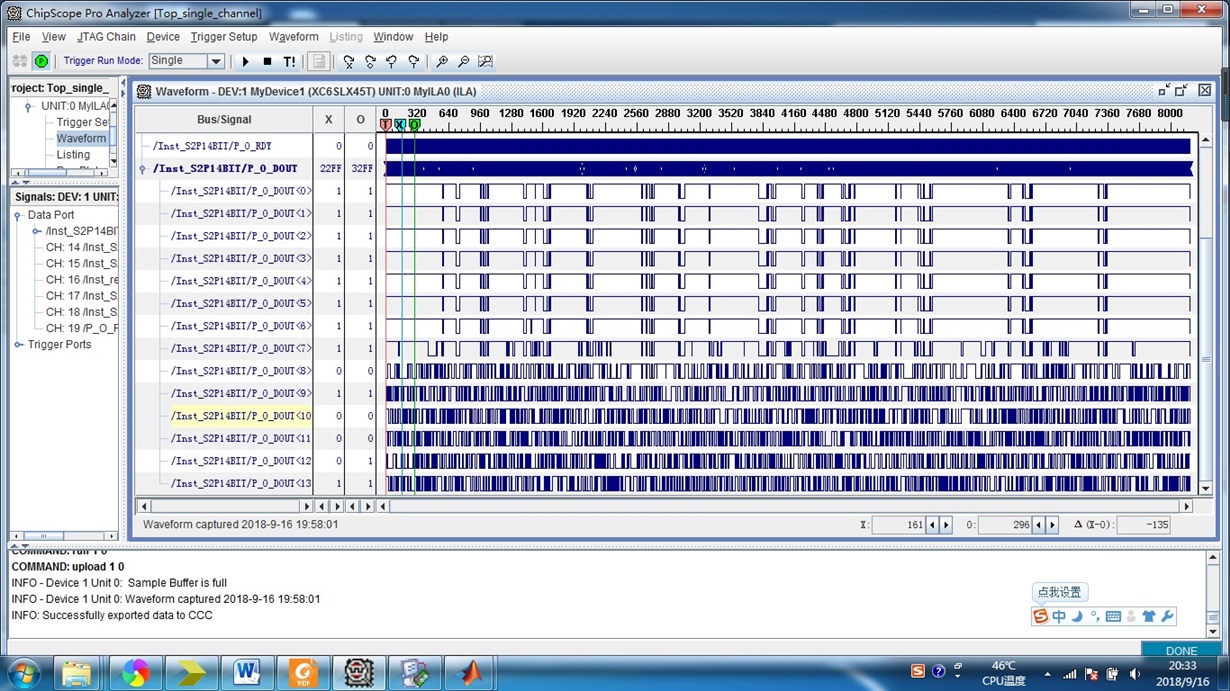

我已经制作了一个使用 AFE5809作为 ADC 的定制板。 我可以通过 FPGA 读取采样数据、并在 CHIPSCOPE (Xilinx IP 内核)中显示波形。

我发现噪声太高、似乎最低的6位只是噪声。 我已经使用5809的 RAMP 彭定康测试了 LVDS 捕获代码、没关系。

5809输入之前没有其他前置放大器级。 输入引脚上的噪声约为10mVpp (更像是示波器的自噪声)

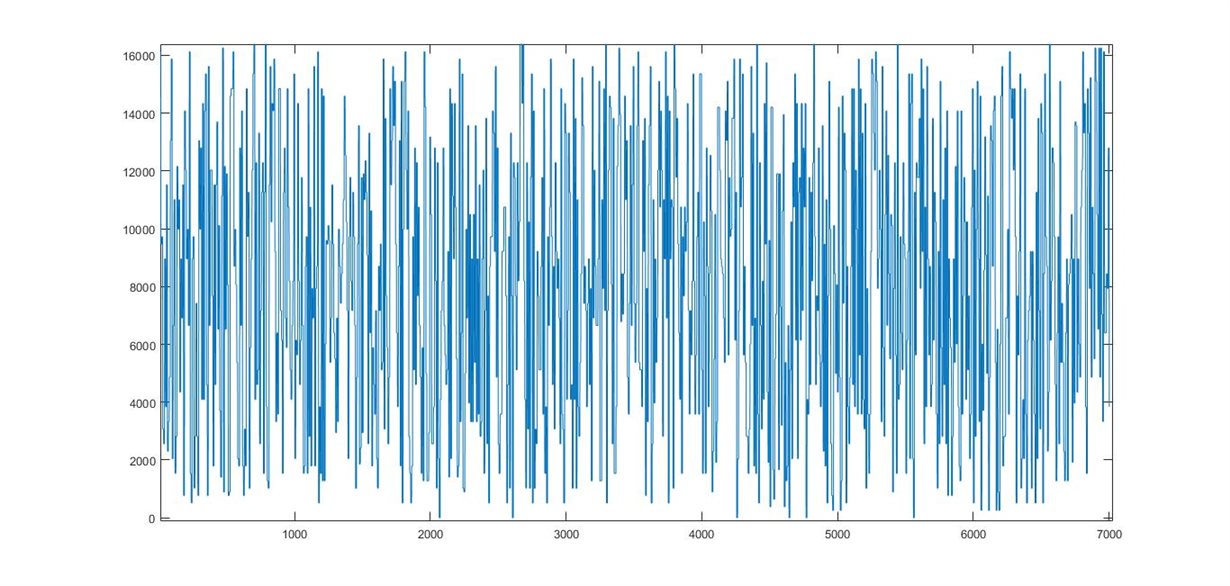

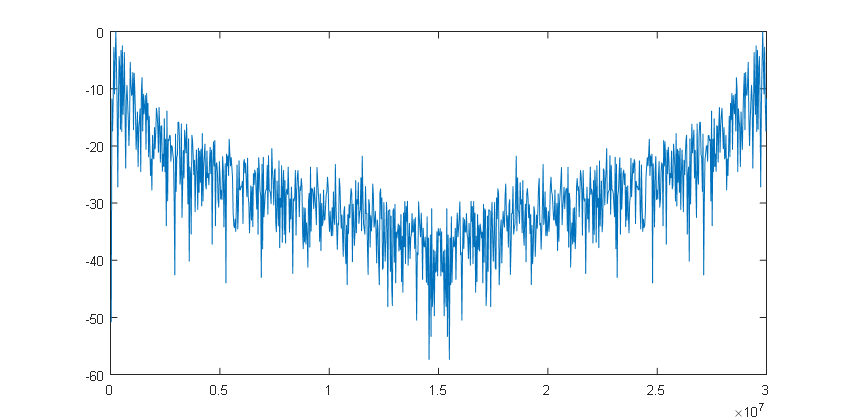

芯片范围中显示的噪声

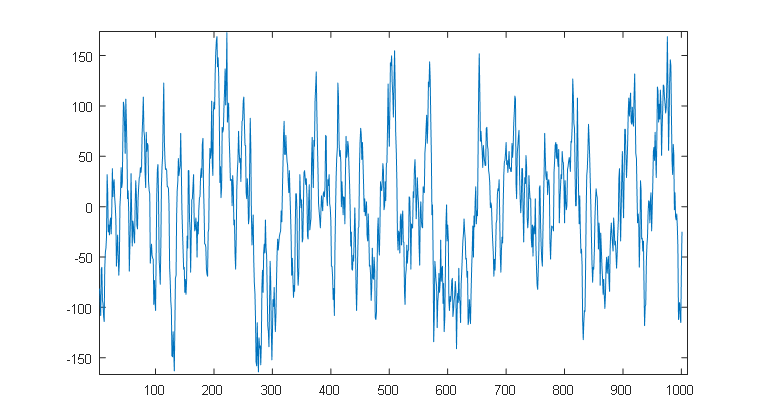

电流噪声

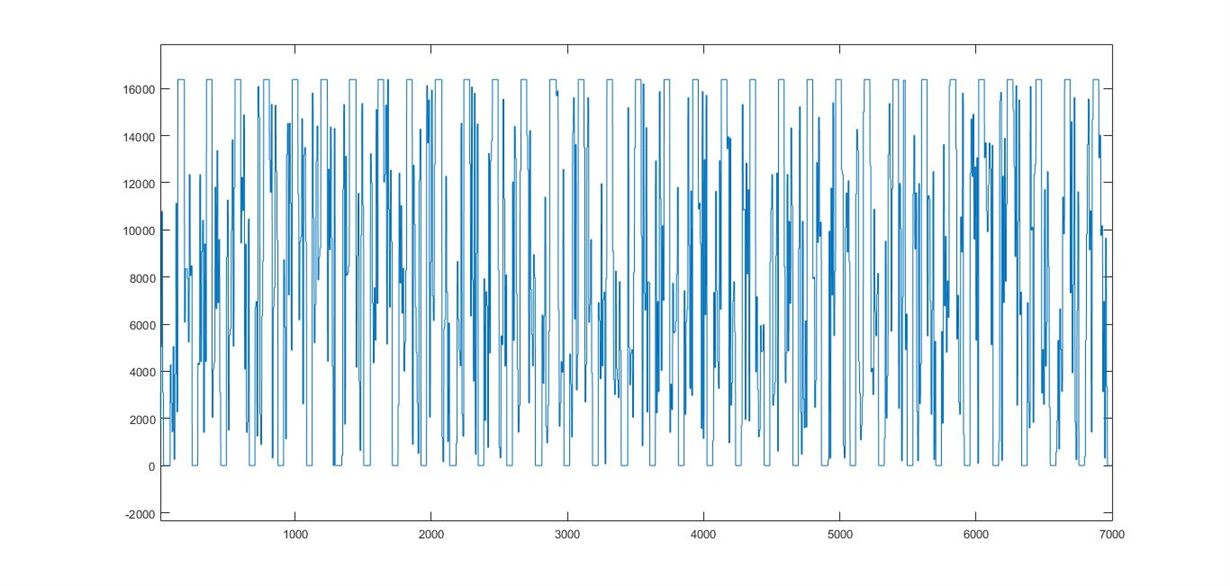

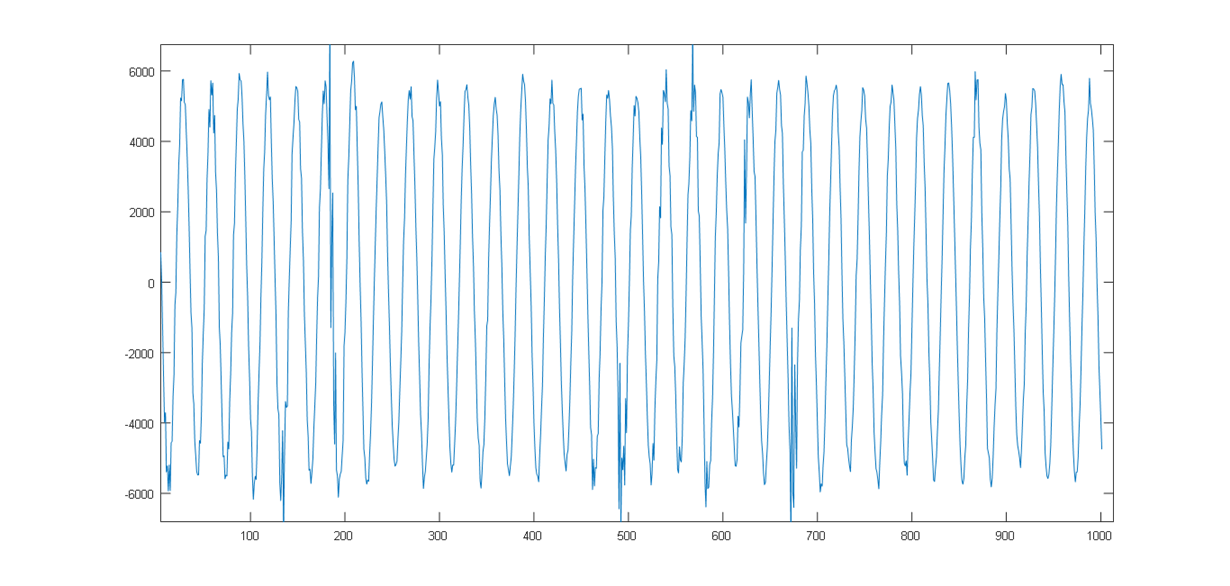

输入端添加40mVpp、1MHz 正弦波时的波形。